CVDLớp phủ SiCđang định hình lại giới hạn của các quy trình sản xuất chất bán dẫn với tốc độ đáng kinh ngạc. Công nghệ phủ có vẻ đơn giản này đã trở thành giải pháp then chốt cho ba thách thức cốt lõi là ô nhiễm hạt, ăn mòn nhiệt độ cao và xói mòn plasma trong sản xuất chip. Các nhà sản xuất thiết bị bán dẫn hàng đầu thế giới đã liệt kê nó là công nghệ tiêu chuẩn cho thiết bị thế hệ tiếp theo. Vậy, điều gì khiến lớp phủ này trở thành "lớp áo giáp vô hình" của sản xuất chip? Bài viết này sẽ phân tích sâu sắc các nguyên tắc kỹ thuật, ứng dụng cốt lõi và những đột phá tiên tiến của nó.

Ⅰ. Định nghĩa về lớp phủ CVD SiC

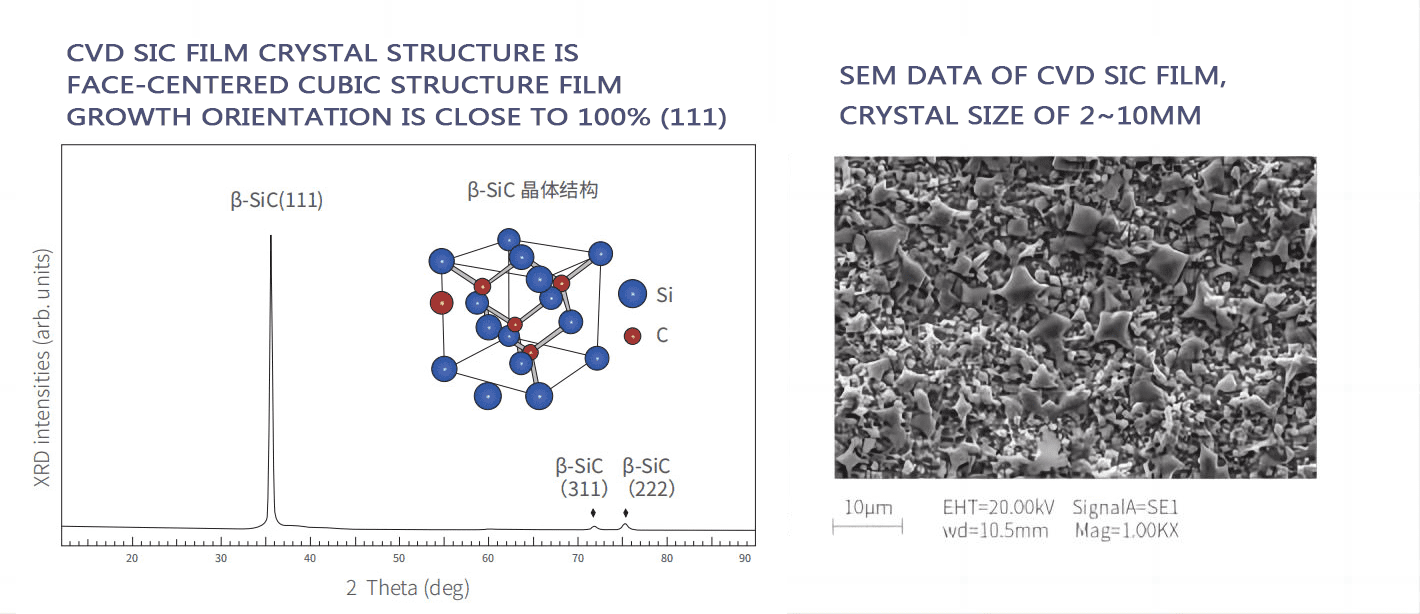

Lớp phủ CVD SiC là lớp bảo vệ của silicon carbide (SiC) được lắng đọng trên một chất nền bằng quy trình lắng đọng hơi hóa học (CVD). Silicon carbide là hợp chất của silicon và carbon, được biết đến với độ cứng tuyệt vời, độ dẫn nhiệt cao, tính trơ về mặt hóa học và khả năng chịu nhiệt độ cao. Công nghệ CVD có thể tạo ra lớp SiC có độ tinh khiết cao, dày đặc và độ dày đồng đều, và có thể phù hợp cao với các hình dạng phức tạp. Điều này làm cho lớp phủ CVD SiC rất phù hợp cho các ứng dụng đòi hỏi khắt khe mà các vật liệu khối truyền thống hoặc các phương pháp phủ khác không thể đáp ứng được.

Ⅱ. Nguyên lý quá trình CVD

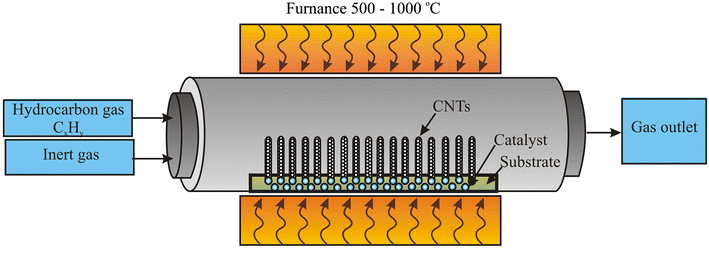

Lắng đọng hơi hóa học (CVD) là một phương pháp sản xuất đa năng được sử dụng để sản xuất vật liệu rắn chất lượng cao, hiệu suất cao. Nguyên lý cốt lõi của CVD liên quan đến phản ứng của các tiền chất khí trên bề mặt của chất nền được nung nóng để tạo thành lớp phủ rắn.

Sau đây là bản phân tích đơn giản về quy trình CVD SiC:

Sơ đồ nguyên lý quá trình CVD

1. Giới thiệu tiền thân:Các tiền chất dạng khí, thường là khí chứa silicon (ví dụ, methyltrichlorosilane – MTS hoặc silane – SiH₄) và khí chứa carbon (ví dụ, propane – C₃H₈), được đưa vào buồng phản ứng.

2. Giao khí:Các khí tiền thân này chảy qua chất nền được đun nóng.

3. Sự hấp thụ: Các phân tử tiền chất hấp thụ vào bề mặt của chất nền nóng.

4. Phản ứng bề mặt: Ở nhiệt độ cao, các phân tử hấp phụ trải qua phản ứng hóa học, dẫn đến sự phân hủy tiền chất và hình thành lớp màng SiC rắn. Các sản phẩm phụ được giải phóng dưới dạng khí.

5. Giải hấp và xả thải: Các sản phẩm phụ dạng khí tách khỏi bề mặt và sau đó thoát ra khỏi buồng. Kiểm soát chính xác nhiệt độ, áp suất, lưu lượng khí và nồng độ tiền chất là rất quan trọng để đạt được các đặc tính màng mong muốn, bao gồm độ dày, độ tinh khiết, độ kết tinh và độ bám dính.

Ⅲ. Ứng dụng của lớp phủ CVD SiC trong quy trình bán dẫn

Lớp phủ CVD SiC không thể thiếu trong sản xuất chất bán dẫn vì sự kết hợp độc đáo của các đặc tính của chúng đáp ứng trực tiếp các điều kiện khắc nghiệt và các yêu cầu nghiêm ngặt về độ tinh khiết của môi trường sản xuất. Chúng tăng cường khả năng chống ăn mòn plasma, tấn công hóa học và tạo hạt, tất cả đều rất quan trọng để tối đa hóa năng suất wafer và thời gian hoạt động của thiết bị.

Sau đây là một số bộ phận phủ CVD SiC phổ biến và các ứng dụng của chúng:

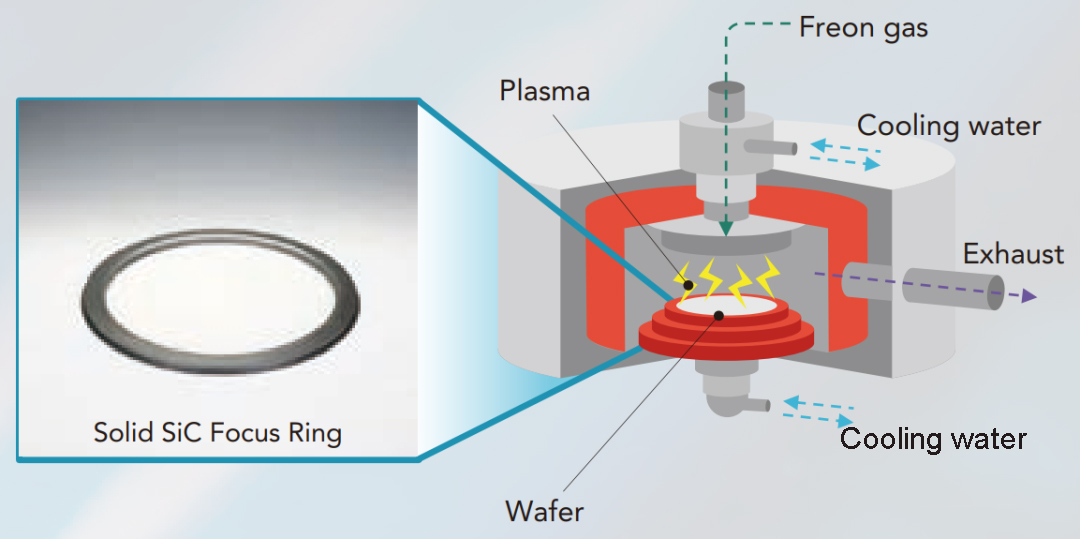

1. Buồng khắc Plasma và vòng hội tụ

Các sản phẩm: Lớp lót, vòi hoa sen, bộ phận cảm ứng và vòng lấy nét được phủ CVD SiC.

Ứng dụng: Trong quá trình khắc plasma, plasma hoạt động mạnh được sử dụng để loại bỏ có chọn lọc các vật liệu khỏi wafer. Các vật liệu không phủ hoặc kém bền sẽ nhanh chóng bị phân hủy, dẫn đến ô nhiễm hạt và thời gian chết thường xuyên. Lớp phủ CVD SiC có khả năng chống lại các hóa chất plasma mạnh (ví dụ: plasma flo, clo, brom), kéo dài tuổi thọ của các thành phần buồng chính và giảm sự hình thành hạt, giúp tăng trực tiếp năng suất wafer.

2.Buồng PECVD và HDPCVD

Các sản phẩm: Buồng phản ứng và điện cực phủ CVD SiC.

Ứng dụng: Lắng đọng hơi hóa học tăng cường plasma (PECVD) và CVD plasma mật độ cao (HDPCVD) được sử dụng để lắng đọng các màng mỏng (ví dụ: lớp điện môi, lớp thụ động). Các quy trình này cũng liên quan đến môi trường plasma khắc nghiệt. Lớp phủ CVD SiC bảo vệ thành buồng và điện cực khỏi bị xói mòn, đảm bảo chất lượng màng đồng nhất và giảm thiểu khuyết tật.

3. Thiết bị cấy ion

Các sản phẩm: Các thành phần chùm tia được phủ CVD SiC (ví dụ: lỗ thông hơi, cốc Faraday).

Ứng dụng: Cấy ion đưa các ion pha tạp vào các chất nền bán dẫn. Các chùm ion năng lượng cao có thể gây ra hiện tượng phun và xói mòn các thành phần tiếp xúc. Độ cứng và độ tinh khiết cao của CVD SiC làm giảm sự tạo thành hạt từ các thành phần đường chùm, ngăn ngừa ô nhiễm các tấm wafer trong bước pha tạp quan trọng này.

4. Các thành phần lò phản ứng epitaxial

Các sản phẩm: Bộ phận phân phối khí và bộ phận tiếp nhận phủ CVD SiC.

Ứng dụng: Phát triển epitaxial (EPI) liên quan đến việc phát triển các lớp tinh thể có trật tự cao trên một chất nền ở nhiệt độ cao. Các susceptor phủ CVD SiC cung cấp độ ổn định nhiệt và trơ về mặt hóa học tuyệt vời ở nhiệt độ cao, đảm bảo gia nhiệt đồng đều và ngăn ngừa nhiễm bẩn cho chính susceptor, điều này rất quan trọng để đạt được các lớp epitaxial chất lượng cao.

Khi hình dạng chip thu hẹp và nhu cầu xử lý tăng cao, nhu cầu về nhà cung cấp lớp phủ CVD SiC chất lượng cao và nhà sản xuất lớp phủ CVD tiếp tục tăng.

IV. Những thách thức của quy trình phủ CVD SiC là gì?

Mặc dù lớp phủ CVD SiC có nhiều ưu điểm lớn, nhưng quá trình sản xuất và ứng dụng của nó vẫn phải đối mặt với một số thách thức về quy trình. Giải quyết những thách thức này là chìa khóa để đạt được hiệu suất ổn định và hiệu quả về chi phí.

Thách thức:

1. Độ bám dính vào chất nền

SiC có thể gặp khó khăn trong việc đạt được độ bám dính mạnh và đồng đều với nhiều vật liệu nền khác nhau (ví dụ: than chì, silicon, gốm) do sự khác biệt về hệ số giãn nở nhiệt và năng lượng bề mặt. Độ bám dính kém có thể dẫn đến tách lớp trong quá trình tuần hoàn nhiệt hoặc ứng suất cơ học.

Giải pháp:

Chuẩn bị bề mặt: Làm sạch và xử lý bề mặt cẩn thận (ví dụ, khắc, xử lý plasma) của chất nền để loại bỏ chất gây ô nhiễm và tạo ra bề mặt tối ưu cho việc liên kết.

Lớp xen kẽ: Phủ một lớp đệm hoặc lớp xen kẽ mỏng và tùy chỉnh (ví dụ: carbon nhiệt phân, TaC – tương tự như lớp phủ CVD TaC trong các ứng dụng cụ thể) để giảm thiểu sự không khớp giãn nở nhiệt và thúc đẩy độ bám dính.

Tối ưu hóa các thông số lắng đọng: Kiểm soát cẩn thận nhiệt độ lắng đọng, áp suất và tỷ lệ khí để tối ưu hóa quá trình hình thành và phát triển của màng SiC và thúc đẩy liên kết giao diện mạnh mẽ.

2. Căng thẳng và nứt màng phim

Trong quá trình lắng đọng hoặc làm nguội sau đó, ứng suất dư có thể phát triển bên trong màng SiC, gây nứt hoặc cong vênh, đặc biệt là trên các hình dạng lớn hoặc phức tạp.

Giải pháp:

Kiểm soát nhiệt độ: Kiểm soát chính xác tốc độ gia nhiệt và làm mát để giảm thiểu sốc nhiệt và ứng suất.

Lớp phủ Gradient:Sử dụng phương pháp phủ nhiều lớp hoặc phủ theo độ dốc để dần dần thay đổi thành phần hoặc cấu trúc vật liệu để thích ứng với ứng suất.

Ủ sau khi lắng đọng: Ủ các bộ phận được phủ để loại bỏ ứng suất còn lại và cải thiện tính toàn vẹn của màng phủ.

3. Sự phù hợp và tính đồng nhất trên hình học phức tạp

Việc lắng đọng lớp phủ đồng đều và có độ dày phù hợp trên các bộ phận có hình dạng phức tạp, tỷ lệ khung hình cao hoặc kênh bên trong có thể gặp khó khăn do hạn chế về động học phản ứng và khuếch tán tiền chất.

Giải pháp:

Tối ưu hóa thiết kế lò phản ứng: Thiết kế lò phản ứng CVD với động lực dòng khí được tối ưu hóa và nhiệt độ đồng đều để đảm bảo phân phối đồng đều các tiền chất.

Điều chỉnh tham số quy trình: Điều chỉnh chính xác áp suất lắng đọng, tốc độ dòng chảy và nồng độ tiền chất để tăng cường sự khuếch tán pha khí vào các đặc điểm phức tạp.

Lắng đọng nhiều giai đoạn: Sử dụng các bước lắng đọng liên tục hoặc thiết bị cố định quay để đảm bảo tất cả các bề mặt đều được phủ đầy đủ.

V. Câu hỏi thường gặp

Câu hỏi 1: Sự khác biệt cốt lõi giữa CVD SiC và PVD SiC trong ứng dụng bán dẫn là gì?

A: Lớp phủ CVD là cấu trúc tinh thể dạng cột có độ tinh khiết >99,99%, phù hợp với môi trường plasma; lớp phủ PVD chủ yếu là dạng vô định hình/nano tinh thể có độ tinh khiết <99,9%, chủ yếu được sử dụng làm lớp phủ trang trí.

Câu 2: Nhiệt độ tối đa mà lớp phủ có thể chịu được là bao nhiêu?

A: Dung sai ngắn hạn ở mức 1650°C (như quá trình ủ), giới hạn sử dụng dài hạn ở mức 1450°C, vượt quá nhiệt độ này sẽ gây ra sự chuyển pha từ β-SiC sang α-SiC.

Câu hỏi 3: Phạm vi độ dày lớp phủ điển hình?

A: Các thành phần bán dẫn chủ yếu có kích thước 80-150μm và lớp phủ EBC của động cơ máy bay có thể đạt tới 300-500μm.

Câu 4: Những yếu tố chính ảnh hưởng đến chi phí là gì?

A: Độ tinh khiết của tiền chất (40%), mức tiêu thụ năng lượng của thiết bị (30%), tổn thất năng suất (20%). Giá đơn vị của lớp phủ cao cấp có thể lên tới 5.000 đô la/kg.

Câu 5: Các nhà cung cấp lớn trên toàn cầu là gì?

A: Châu Âu và Hoa Kỳ: CoorsTek, Mersen, Ionbond; Châu Á: Semixlab, Veteksemicon, Kallex (Đài Loan), Scientech (Đài Loan)

Thời gian đăng: 09-06-2025