CVDPowłoka SiCzmienia granice procesów produkcji półprzewodników w zadziwiającym tempie. Ta pozornie prosta technologia powlekania stała się kluczowym rozwiązaniem trzech głównych wyzwań: zanieczyszczenia cząsteczkami, korozji wysokotemperaturowej i erozji plazmowej w produkcji chipów. Najwięksi światowi producenci sprzętu półprzewodnikowego wymienili ją jako standardową technologię dla sprzętu nowej generacji. Co zatem sprawia, że ta powłoka jest „niewidzialną zbroją” produkcji chipów? W tym artykule dogłębnie przeanalizujemy jej zasady techniczne, główne zastosowania i przełomowe osiągnięcia.

I. Definicja powłoki CVD SiC

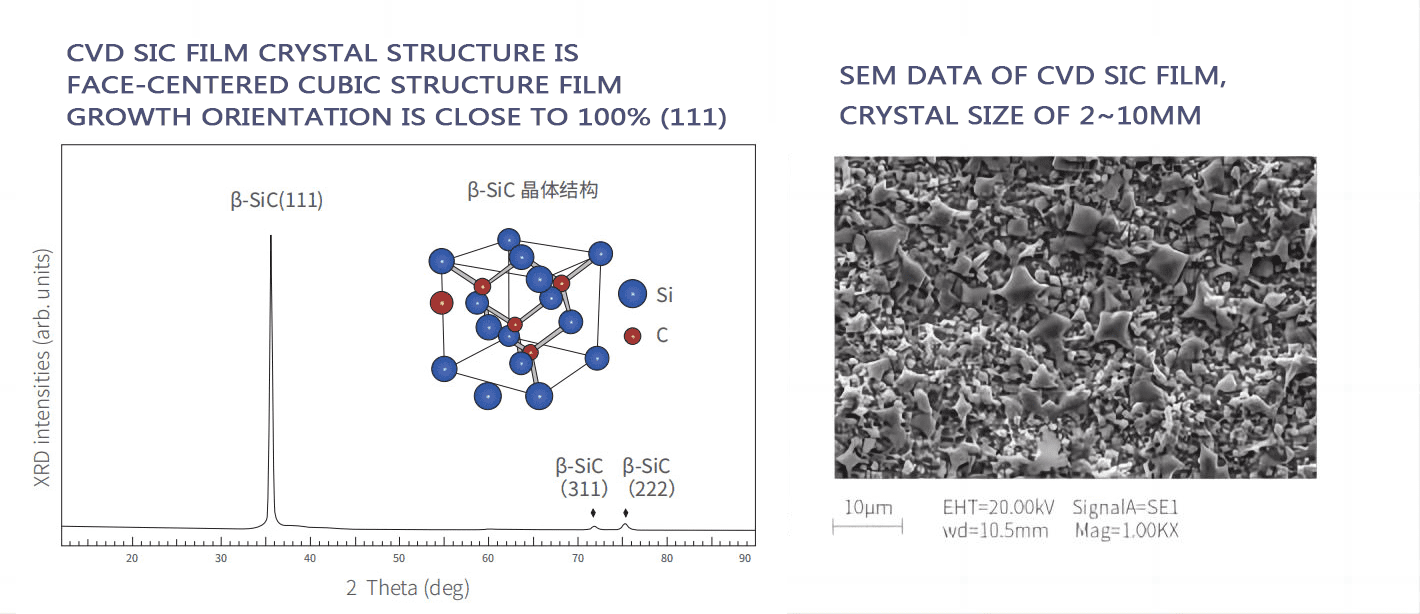

Powłoka CVD SiC odnosi się do warstwy ochronnej węglika krzemu (SiC) osadzonej na podłożu w procesie chemicznego osadzania z fazy gazowej (CVD). Węglik krzemu to związek krzemu i węgla, znany ze swojej doskonałej twardości, wysokiej przewodności cieplnej, obojętności chemicznej i odporności na wysoką temperaturę. Technologia CVD może tworzyć warstwę SiC o wysokiej czystości, gęstości i jednolitej grubości, a także może być wysoce konformalna do złożonych geometrii. Dzięki temu powłoki CVD SiC są bardzo odpowiednie do wymagających zastosowań, których nie można spełnić za pomocą tradycyjnych materiałów masowych lub innych metod powlekania.

II. Zasada procesu CVD

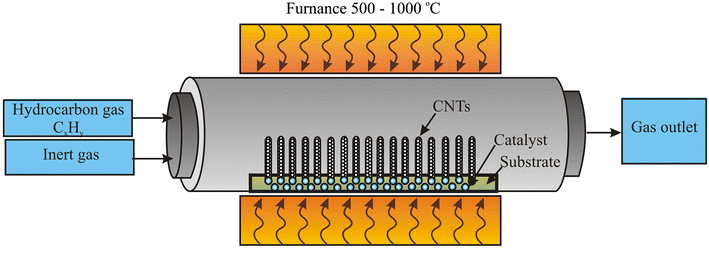

Osadzanie chemiczne z fazy gazowej (CVD) to wszechstronna metoda produkcji stosowana do wytwarzania wysokiej jakości, wysoko wydajnych materiałów stałych. Podstawowa zasada CVD obejmuje reakcję gazowych prekursorów na powierzchni ogrzanego podłoża w celu utworzenia stałej powłoki.

Poniżej przedstawiono uproszczony opis procesu CVD z SiC:

Schemat zasady procesu CVD

1. Wprowadzenie prekursora:Do komory reakcyjnej wprowadza się prekursory gazowe, zazwyczaj gazy zawierające krzem (np. metylotrichlorosilan – MTS lub silan – SiH₄) i gazy zawierające węgiel (np. propan – C₃H₈).

2. Dostawa gazu:Te gazy prekursorowe przepływają nad ogrzanym podłożem.

3. Adsorpcja:Cząsteczki prekursorowe ulegają adsorpcji na powierzchni gorącego podłoża.

4. Reakcja powierzchniowa:W wysokich temperaturach zaadsorbowane cząsteczki ulegają reakcjom chemicznym, co powoduje rozkład prekursora i utworzenie stałej warstwy SiC. Produkty uboczne są uwalniane w postaci gazów.

5. Desorpcja i wydech: Produkty uboczne w postaci gazu desorpują z powierzchni, a następnie są odprowadzane z komory. Precyzyjna kontrola temperatury, ciśnienia, szybkości przepływu gazu i stężenia prekursora ma kluczowe znaczenie dla uzyskania pożądanych właściwości folii, w tym grubości, czystości, krystaliczności i przyczepności.

III. Zastosowanie powłok CVD SiC w procesach półprzewodnikowych

Powłoki CVD SiC są niezbędne w produkcji półprzewodników, ponieważ ich unikalna kombinacja właściwości bezpośrednio spełnia ekstremalne warunki i surowe wymagania czystości środowiska produkcyjnego. Zwiększają odporność na korozję plazmową, atak chemiczny i generowanie cząstek, które są krytyczne dla maksymalizacji wydajności płytek i czasu sprawności urządzeń.

Poniżej przedstawiono kilka powszechnie stosowanych części powlekanych CVD SiC i ich zastosowania:

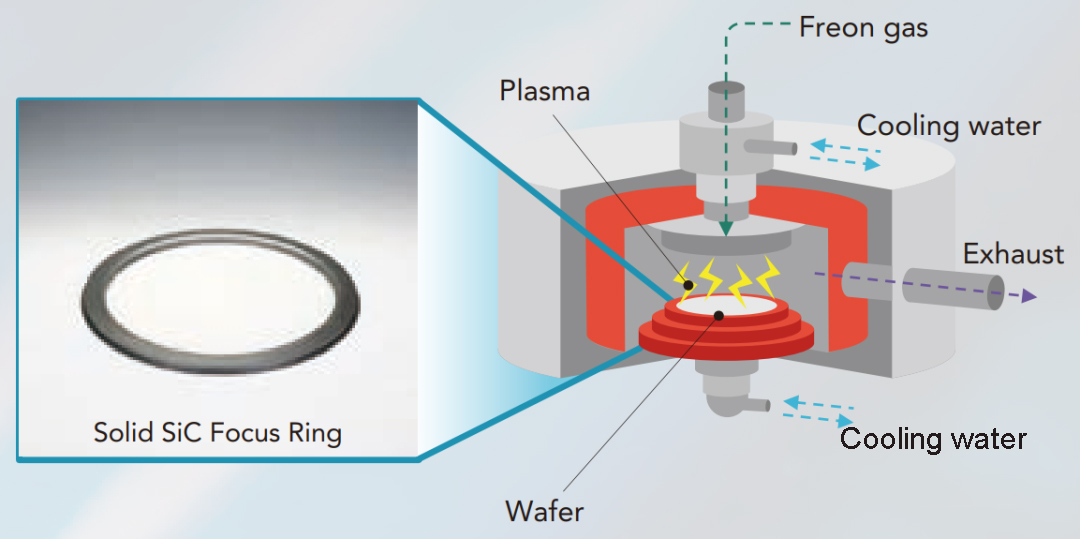

1. Komora trawienia plazmowego i pierścień ogniskujący

Produkty:Wkładki, głowice natryskowe, susceptory i pierścienie ogniskujące pokryte powłoką CVD SiC.

Aplikacja: W trawieniu plazmowym do selektywnego usuwania materiałów z płytek stosuje się wysoce aktywną plazmę. Materiały niepowlekane lub mniej trwałe ulegają szybkiej degradacji, co powoduje zanieczyszczenie cząsteczkami i częste przestoje. Powłoki CVD SiC charakteryzują się doskonałą odpornością na agresywne substancje chemiczne plazmy (np. plazmy fluoru, chloru, bromu), wydłużają żywotność kluczowych elementów komory i zmniejszają generowanie cząsteczek, co bezpośrednio zwiększa wydajność płytek.

2. Komory PECVD i HDPCVD

Produkty: Komory reakcyjne i elektrody pokryte CVD SiC.

Aplikacje: Do osadzania cienkich warstw (np. warstw dielektrycznych, warstw pasywacyjnych) stosuje się osadzanie chemiczne z fazy gazowej wspomagane plazmą (PECVD) i osadzanie plazmowe CVD o wysokiej gęstości (HDPCVD). Procesy te obejmują również trudne warunki plazmowe. Powłoki CVD SiC chronią ściany komory i elektrody przed erozją, zapewniając stałą jakość powłoki i minimalizując defekty.

3. Sprzęt do implantacji jonów

Produkty:Elementy linii wiązkowej pokryte powłoką CVD SiC (np. apertury, kubki Faradaya).

Aplikacje:Implantacja jonowa wprowadza jony domieszkowe do podłoży półprzewodnikowych. Wysokoenergetyczne wiązki jonów mogą powodować rozpryskiwanie i erozję odsłoniętych komponentów. Twardość i wysoka czystość CVD SiC zmniejszają generowanie cząstek z komponentów linii wiązki, zapobiegając zanieczyszczeniu płytek podczas tego krytycznego etapu domieszkowania.

4. Elementy reaktora epitaksjalnego

Produkty:Susceptory i rozdzielacze gazu pokryte powłoką CVD SiC.

Aplikacje:Wzrost epitaksjalny (EPI) obejmuje wzrost wysoce uporządkowanych warstw krystalicznych na podłożu w wysokich temperaturach. Susceptory pokryte CVD SiC oferują doskonałą stabilność termiczną i obojętność chemiczną w wysokich temperaturach, zapewniając równomierne ogrzewanie i zapobiegając zanieczyszczeniu samego susceptora, co jest krytyczne dla uzyskania wysokiej jakości warstw epitaksjalnych.

W miarę jak geometria układów scalonych ulega zmniejszeniu, a wymagania dotyczące przetwarzania rosną, zapotrzebowanie na dostawców wysokiej jakości powłok CVD SiC i producentów powłok CVD stale rośnie.

IV. Jakie są wyzwania procesu powlekania CVD SiC?

Pomimo wielkich zalet powłoki CVD SiC, jej produkcja i zastosowanie wciąż napotykają pewne wyzwania procesowe. Rozwiązanie tych wyzwań jest kluczem do osiągnięcia stabilnej wydajności i opłacalności.

Wyzwania:

1. Przyczepność do podłoża

SiC może być trudne do osiągnięcia, ze względu na różnice współczynników rozszerzalności cieplnej i energii powierzchniowej, do uzyskania silnej i jednolitej przyczepności do różnych materiałów podłoża (np. grafitu, krzemu, ceramiki). Słaba przyczepność może prowadzić do rozwarstwienia podczas cykli termicznych lub naprężeń mechanicznych.

Rozwiązania:

Przygotowanie powierzchni:Dokładne czyszczenie i obróbka powierzchni (np. trawienie, obróbka plazmowa) podłoża w celu usunięcia zanieczyszczeń i stworzenia optymalnej powierzchni do łączenia.

Międzywarstwa: Nałóż cienką i dostosowaną warstwę pośrednią lub buforową (np. węgiel pirolityczny, TaC – podobny do powłoki CVD TaC w określonych zastosowaniach), aby złagodzić niedopasowanie rozszerzalności cieplnej i zwiększyć przyczepność.

Optymalizacja parametrów depozycji:Należy starannie kontrolować temperaturę osadzania, ciśnienie i stosunek gazów w celu optymalizacji zarodkowania i wzrostu warstw SiC oraz promowania silnego wiązania międzyfazowego.

2. Naprężenie i pękanie folii

Podczas osadzania lub późniejszego chłodzenia w warstwach SiC mogą powstawać naprężenia szczątkowe powodujące pęknięcia lub odkształcenia, zwłaszcza w przypadku większych lub złożonych geometrii.

Rozwiązania:

Kontrola temperatury:Precyzyjna kontrola szybkości nagrzewania i chłodzenia w celu zminimalizowania szoku termicznego i naprężeń.

Powłoka gradientowa:Wykorzystuj metody powlekania wielowarstwowego lub gradientowego, aby stopniowo zmieniać skład lub strukturę materiału, aby dostosować go do naprężeń.

Wyżarzanie po osadzeniu: Wyżarzanie powlekanych części w celu wyeliminowania naprężeń szczątkowych i poprawy integralności powłoki.

3. Zgodność i jednorodność w złożonych geometriach

Nakładanie równomiernie grubych i zgodnych powłok na części o skomplikowanych kształtach, dużym współczynniku kształtu lub wewnętrznych kanałach może być trudne ze względu na ograniczenia dyfuzji prekursorów i kinetyki reakcji.

Rozwiązania:

Optymalizacja projektu reaktora:Projektowanie reaktorów CVD z optymalizacją dynamiki przepływu gazu i jednorodnością temperatury w celu zapewnienia równomiernego rozkładu prekursorów.

Regulacja parametrów procesu:Dokładne dostrojenie ciśnienia osadzania, szybkości przepływu i stężenia prekursora w celu zwiększenia dyfuzji fazy gazowej do złożonych struktur.

Osadzanie wieloetapowe: Stosuj ciągłe etapy osadzania lub obrotowe urządzenia, aby mieć pewność, że wszystkie powierzchnie zostaną odpowiednio pokryte.

V. Często zadawane pytania

P1: Jaka jest zasadnicza różnica między CVD SiC i PVD SiC w zastosowaniach półprzewodnikowych?

A: Powłoki CVD to kolumnowe struktury krystaliczne o czystości >99,99%, odpowiednie do środowisk plazmowych; powłoki PVD są w większości amorficzne/nanokrystaliczne o czystości <99,9%, stosowane głównie do powłok dekoracyjnych.

P2: Jaka jest maksymalna temperatura, jaką może wytrzymać powłoka?

A: Krótkotrwała tolerancja 1650°C (np. w procesie wyżarzania), długotrwała granica użytkowania 1450°C; przekroczenie tej temperatury spowoduje przemianę fazową z β-SiC w α-SiC.

P3: Jaki jest typowy zakres grubości powłoki?

A: Elementy półprzewodnikowe mają przeważnie grubość 80–150 μm, a powłoki EBC silników lotniczych mogą mieć grubość 300–500 μm.

P4: Jakie są główne czynniki wpływające na koszty?

A: Czystość prekursora (40%), zużycie energii przez sprzęt (30%), strata wydajności (20%). Cena jednostkowa powłok high-end może osiągnąć 5000 USD/kg.

P5: Jacy są główni globalni dostawcy?

A: Europa i Stany Zjednoczone: CoorsTek, Mersen, Ionbond; Azja: Semixlab, Veteksemicon, Kallex (Tajwan), Scientech (Tajwan)

Czas publikacji: 09-06-2025