Những khó khăn về mặt kỹ thuật trong việc sản xuất hàng loạt các tấm silicon carbide chất lượng cao có hiệu suất ổn định bao gồm:

1) Vì tinh thể cần phải phát triển trong môi trường kín có nhiệt độ cao trên 2000°C nên yêu cầu kiểm soát nhiệt độ cực kỳ cao;

2) Vì silicon carbide có hơn 200 cấu trúc tinh thể, nhưng chỉ có một số ít cấu trúc của silicon carbide đơn tinh thể là vật liệu bán dẫn cần thiết, nên tỷ lệ silicon-carbon, gradient nhiệt độ tăng trưởng và sự phát triển tinh thể cần được kiểm soát chính xác trong quá trình phát triển tinh thể. Các thông số như tốc độ và áp suất luồng không khí;

3) Theo phương pháp truyền pha hơi, công nghệ mở rộng đường kính của quá trình phát triển tinh thể silicon carbide cực kỳ khó khăn;

4) Độ cứng của silicon carbide gần bằng kim cương và kỹ thuật cắt, mài và đánh bóng rất khó khăn.

Tấm wafer epitaxy SiC: thường được sản xuất bằng phương pháp lắng đọng hơi hóa học (CVD). Theo các loại pha tạp khác nhau, chúng được chia thành wafer epitaxy loại n và loại p. Hantian Tiancheng và Dongguan Tianyu trong nước hiện có thể cung cấp wafer epitaxy SiC 4 inch/6 inch. Đối với epitaxy SiC, rất khó kiểm soát trong trường điện áp cao và chất lượng epitaxy SiC có tác động lớn hơn đến các thiết bị SiC. Hơn nữa, thiết bị epitaxy được độc quyền bởi bốn công ty hàng đầu trong ngành: Axitron, LPE, TEL và Nuflare.

Silic cacbua epitaxywafer là wafer silicon carbide trong đó một màng tinh thể đơn (lớp epitaxial) với các yêu cầu nhất định và giống như tinh thể nền được phát triển trên nền silicon carbide ban đầu. Phát triển epitaxial chủ yếu sử dụng thiết bị CVD (Chemical Vapor Deposition, ) hoặc thiết bị MBE (Molecular Beam Epitaxy). Vì các thiết bị silicon carbide được sản xuất trực tiếp trong lớp epitaxial, nên chất lượng của lớp epitaxial ảnh hưởng trực tiếp đến hiệu suất và năng suất của thiết bị. Khi hiệu suất chịu điện áp của thiết bị tiếp tục tăng, độ dày của lớp epitaxial tương ứng trở nên dày hơn và việc kiểm soát trở nên khó khăn hơn. Nói chung, khi điện áp khoảng 600V, độ dày lớp epitaxial cần thiết là khoảng 6 micron; khi điện áp trong khoảng 1200-1700V, độ dày lớp epitaxial cần thiết đạt 10-15 micron. Nếu điện áp đạt hơn 10.000 vôn, độ dày lớp epitaxial có thể cần thiết là hơn 100 micron. Khi độ dày của lớp epitaxial tiếp tục tăng, việc kiểm soát độ dày, độ đồng đều về điện trở suất và mật độ khuyết tật ngày càng trở nên khó khăn.

Thiết bị SiC: Trên thế giới, SiC SBD và MOSFET 600~1700V đã được công nghiệp hóa. Các sản phẩm chính thống hoạt động ở mức điện áp dưới 1200V và chủ yếu áp dụng bao bì TO. Về giá cả, các sản phẩm SiC trên thị trường quốc tế có giá cao hơn khoảng 5-6 lần so với các sản phẩm Si tương tự. Tuy nhiên, giá đang giảm với tốc độ hàng năm là 10%. Với việc mở rộng sản xuất vật liệu và thiết bị thượng nguồn trong 2-3 năm tới, nguồn cung thị trường sẽ tăng lên, dẫn đến giá giảm hơn nữa. Dự kiến khi giá đạt 2-3 lần so với sản phẩm Si, những lợi thế do chi phí hệ thống giảm và hiệu suất được cải thiện sẽ dần đưa SiC chiếm lĩnh không gian thị trường của các thiết bị Si.

Bao bì truyền thống dựa trên các chất nền gốc silicon, trong khi vật liệu bán dẫn thế hệ thứ ba đòi hỏi một thiết kế hoàn toàn mới. Sử dụng các cấu trúc bao bì gốc silicon truyền thống cho các thiết bị điện có khoảng cách băng thông rộng có thể gây ra các vấn đề và thách thức mới liên quan đến tần số, quản lý nhiệt và độ tin cậy. Các thiết bị điện SiC nhạy cảm hơn với điện dung ký sinh và độ tự cảm. So với các thiết bị Si, chip điện SiC có tốc độ chuyển mạch nhanh hơn, có thể dẫn đến quá tải, dao động, tăng tổn thất chuyển mạch và thậm chí là trục trặc thiết bị. Ngoài ra, các thiết bị điện SiC hoạt động ở nhiệt độ cao hơn, đòi hỏi các kỹ thuật quản lý nhiệt tiên tiến hơn.

Nhiều cấu trúc khác nhau đã được phát triển trong lĩnh vực đóng gói nguồn bán dẫn có khoảng cách băng thông rộng. Đóng gói mô-đun nguồn dựa trên Si truyền thống không còn phù hợp nữa. Để giải quyết các vấn đề về thông số ký sinh cao và hiệu suất tản nhiệt kém của đóng gói mô-đun nguồn dựa trên Si truyền thống, đóng gói mô-đun nguồn SiC áp dụng công nghệ kết nối không dây và làm mát hai mặt trong cấu trúc của nó, đồng thời áp dụng vật liệu nền có độ dẫn nhiệt tốt hơn và cố gắng tích hợp tụ điện tách rời, cảm biến nhiệt độ/dòng điện và mạch điều khiển vào cấu trúc mô-đun và phát triển nhiều công nghệ đóng gói mô-đun khác nhau. Hơn nữa, có nhiều rào cản kỹ thuật đối với sản xuất thiết bị SiC và chi phí sản xuất cao.

Các thiết bị silicon carbide được sản xuất bằng cách lắng đọng các lớp epitaxial trên một chất nền silicon carbide thông qua CVD. Quá trình này bao gồm làm sạch, oxy hóa, quang khắc, khắc, loại bỏ chất cản quang, cấy ion, lắng đọng hơi hóa học của silicon nitride, đánh bóng, phun và các bước xử lý tiếp theo để tạo thành cấu trúc thiết bị trên chất nền tinh thể đơn SiC. Các loại chính của thiết bị nguồn SiC bao gồm điốt SiC, bóng bán dẫn SiC và mô-đun nguồn SiC. Do các yếu tố như tốc độ sản xuất vật liệu đầu vào chậm và tỷ lệ năng suất thấp, các thiết bị silicon carbide có chi phí sản xuất tương đối cao.

Ngoài ra, việc sản xuất thiết bị silicon carbide còn gặp một số khó khăn về mặt kỹ thuật:

1) Cần phải phát triển một quy trình cụ thể phù hợp với đặc tính của vật liệu silicon carbide. Ví dụ: SiC có điểm nóng chảy cao, khiến phương pháp khuếch tán nhiệt truyền thống không hiệu quả. Cần phải sử dụng phương pháp pha tạp cấy ion và kiểm soát chính xác các thông số như nhiệt độ, tốc độ gia nhiệt, thời gian và lưu lượng khí; SiC trơ với dung môi hóa học. Nên sử dụng các phương pháp như khắc khô và vật liệu mặt nạ, hỗn hợp khí, kiểm soát độ dốc thành bên, tốc độ khắc, độ nhám thành bên, v.v. nên được tối ưu hóa và phát triển;

2) Việc chế tạo điện cực kim loại trên tấm silicon carbide đòi hỏi điện trở tiếp xúc dưới 10-5Ω2. Vật liệu điện cực đáp ứng yêu cầu, Ni và Al, có độ ổn định nhiệt kém ở trên 100°C, nhưng Al/Ni có độ ổn định nhiệt tốt hơn. Điện trở tiếp xúc riêng của vật liệu điện cực composite /W/Au cao hơn 10-3Ω2;

3) SiC có độ mài mòn cắt cao và độ cứng của SiC chỉ đứng sau kim cương, điều này đặt ra yêu cầu cao hơn về công nghệ cắt, mài, đánh bóng và các công nghệ khác.

Hơn nữa, các thiết bị nguồn silicon carbide rãnh khó sản xuất hơn. Theo các cấu trúc thiết bị khác nhau, các thiết bị nguồn silicon carbide chủ yếu có thể được chia thành các thiết bị phẳng và thiết bị rãnh. Các thiết bị nguồn silicon carbide phẳng có tính nhất quán đơn vị tốt và quy trình sản xuất đơn giản, nhưng dễ bị hiệu ứng JFET và có điện dung ký sinh cao và điện trở trạng thái bật. So với các thiết bị phẳng, các thiết bị nguồn silicon carbide rãnh có tính nhất quán đơn vị thấp hơn và có quy trình sản xuất phức tạp hơn. Tuy nhiên, cấu trúc rãnh có lợi cho việc tăng mật độ đơn vị thiết bị và ít có khả năng tạo ra hiệu ứng JFET, có lợi cho việc giải quyết vấn đề về tính di động của kênh. Nó có các đặc tính tuyệt vời như điện trở bật nhỏ, điện dung ký sinh nhỏ và mức tiêu thụ năng lượng chuyển mạch thấp. Nó có lợi thế đáng kể về chi phí và hiệu suất và đã trở thành hướng phát triển chính của các thiết bị nguồn silicon carbide. Theo trang web chính thức của Rohm, cấu trúc ROHM Gen3 (cấu trúc rãnh Gen1) chỉ bằng 75% diện tích chip Gen2 (Plannar2) và điện trở khi bật của cấu trúc ROHM Gen3 giảm 50% ở cùng kích thước chip.

Chi phí cho vật liệu nền silicon carbide, epitaxy, front-end, R&D và các chi phí khác lần lượt chiếm 47%, 23%, 19%, 6% và 5% chi phí sản xuất thiết bị silicon carbide.

Cuối cùng, chúng tôi sẽ tập trung vào việc phá bỏ các rào cản kỹ thuật của chất nền trong chuỗi công nghiệp silicon carbide.

Quá trình sản xuất chất nền silicon carbide tương tự như quá trình sản xuất chất nền gốc silicon, nhưng khó khăn hơn.

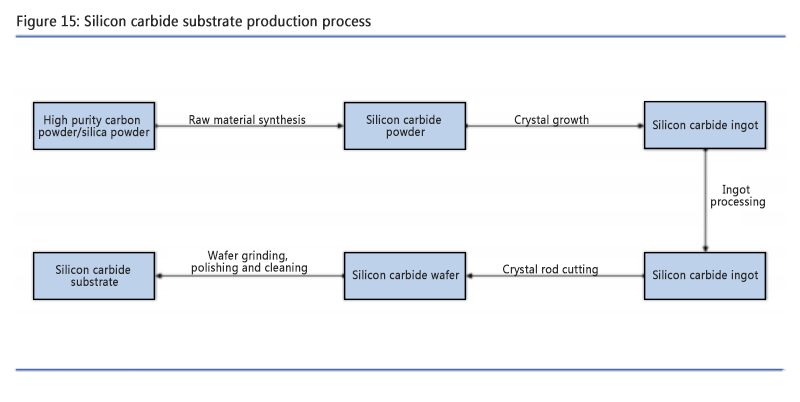

Quy trình sản xuất chất nền silicon carbide thường bao gồm tổng hợp nguyên liệu thô, phát triển tinh thể, xử lý thỏi, cắt thỏi, nghiền wafer, đánh bóng, làm sạch và các khâu khác.

Giai đoạn phát triển tinh thể là cốt lõi của toàn bộ quá trình và bước này quyết định tính chất điện của chất nền silicon carbide.

Vật liệu silicon carbide khó phát triển trong pha lỏng trong điều kiện bình thường. Phương pháp phát triển pha hơi phổ biến trên thị trường hiện nay có nhiệt độ phát triển trên 2300°C và đòi hỏi phải kiểm soát chính xác nhiệt độ phát triển. Toàn bộ quy trình vận hành hầu như khó quan sát. Một lỗi nhỏ sẽ dẫn đến việc loại bỏ sản phẩm. Trong khi đó, vật liệu silicon chỉ cần 1600℃, thấp hơn nhiều. Việc chuẩn bị chất nền silicon carbide cũng gặp phải những khó khăn như tinh thể phát triển chậm và yêu cầu dạng tinh thể cao. Quá trình phát triển wafer silicon carbide mất khoảng 7 đến 10 ngày, trong khi kéo thanh silicon chỉ mất 2 ngày rưỡi. Hơn nữa, silicon carbide là vật liệu có độ cứng chỉ đứng sau kim cương. Nó sẽ mất rất nhiều trong quá trình cắt, mài và đánh bóng và tỷ lệ đầu ra chỉ là 60%.

Chúng tôi biết rằng xu hướng là tăng kích thước của chất nền silicon carbide, khi kích thước tiếp tục tăng, yêu cầu về công nghệ mở rộng đường kính ngày càng cao. Nó đòi hỏi sự kết hợp của nhiều yếu tố kiểm soát kỹ thuật khác nhau để đạt được sự phát triển lặp lại của tinh thể.

Thời gian đăng: 22-05-2024