安定した性能を持つ高品質のシリコンカーバイドウェハを安定的に大量生産するための技術的な困難は次のとおりです。

1) 結晶は 2000℃ を超える高温密閉環境で成長する必要があるため、温度制御要件が極めて高くなります。

2)炭化ケイ素には200種類以上の結晶構造がありますが、半導体材料として求められる単結晶炭化ケイ素はごくわずかであるため、結晶成長プロセスにおいては、シリコンと炭素の比率、成長温度勾配、結晶成長を精密に制御する必要があります。速度や空気流圧力などのパラメータも重要です。

3) 気相透過法では、炭化ケイ素結晶成長の直径拡大技術が極めて困難である。

4) 炭化ケイ素の硬度はダイヤモンドに近く、切断、研削、研磨の技術が難しい。

SiCエピタキシャルウェハ:通常は化学気相成長法(CVD)で製造されます。ドーピングの種類によって、n型とp型のエピタキシャルウェハに分類されます。国内の漢天天成と東莞天宇は、既に4インチ/6インチのSiCエピタキシャルウェハを提供しています。SiCエピタキシャルウェハは、高電圧領域での制御が難しく、SiCエピタキシャルウェハの品質がSiCデバイスに大きな影響を与えます。また、エピタキシャル装置は、業界をリードする4社、Axitron、LPE、TEL、Nuflareによって独占されています。

炭化ケイ素エピタキシャルウェーハとは、炭化ケイ素基板上に、一定の要件を満たし、基板結晶と同じ単結晶膜(エピタキシャル層)を成長させたシリコンカーバイドウェーハを指します。エピタキシャル成長は、主にCVD(化学気相成長)装置またはMBE(分子線エピタキシー)装置を用いて行われます。シリコンカーバイドデバイスはエピタキシャル層で直接製造されるため、エピタキシャル層の品質はデバイスの性能と歩留まりに直接影響します。デバイスの耐圧性能が向上し続けると、対応するエピタキシャル層の厚さが厚くなり、制御が難しくなります。一般に、電圧が約600Vの場合、必要なエピタキシャル層の厚さは約6ミクロンです。電圧が1200〜1700Vの場合、必要なエピタキシャル層の厚さは10〜15ミクロンに達します。電圧が10,000ボルトを超える場合、100ミクロンを超えるエピタキシャル層の厚さが必要になる場合があります。エピタキシャル層の厚さが厚くなるにつれて、厚さと抵抗率の均一性、そして欠陥密度を制御することがますます困難になります。

SiCデバイス:世界的には、600~1700VのSiC SBDとMOSFETが既に産業化されています。主流製品は1200V以下の電圧で動作し、主にTOパッケージを採用しています。価格面では、国際市場におけるSiC製品の価格はSi製品の約5~6倍です。しかし、価格は年率10%で下落しています。今後2~3年で上流材料とデバイス生産が拡大し、市場供給量が増加し、さらなる価格低下が見込まれます。価格がSi製品の2~3倍に達する頃には、システムコストの削減と性能向上によるメリットにより、SiCが徐々にSiデバイスの市場シェアを占めるようになると予想されます。

従来のパッケージはシリコンベースの基板に基づいていますが、第3世代の半導体材料では全く新しい設計が求められます。ワイドバンドギャップパワーデバイスに従来のシリコンベースのパッケージ構造を使用すると、周波数、熱管理、信頼性に関する新たな問題や課題が生じる可能性があります。SiCパワーデバイスは、寄生容量と寄生インダクタンスの影響を受けやすいです。Siデバイスと比較して、SiCパワーチップはスイッチング速度が速いため、オーバーシュート、発振、スイッチング損失の増加、さらにはデバイスの誤動作につながる可能性があります。さらに、SiCパワーデバイスは高温で動作するため、より高度な熱管理技術が必要となります。

ワイドバンドギャップ半導体パワーパッケージングの分野では、様々な構造が開発されてきました。従来のSiベースのパワーモジュールパッケージングはもはや適していません。従来のSiベースのパワーモジュールパッケージングが抱える高い寄生パラメータと低い放熱効率の問題を解決するため、SiCパワーモジュールパッケージングでは、ワイヤレス相互接続と両面冷却技術を構造に採用し、さらに熱伝導性に優れた基板材料を採用し、デカップリングコンデンサ、温度/電流センサー、駆動回路などをモジュール構造に統合するなど、様々なモジュールパッケージング技術が開発されてきました。しかし、SiCデバイスの製造には高い技術的障壁があり、製造コストも高いという課題がありました。

シリコンカーバイドデバイスは、CVD法を用いてシリコンカーバイド基板上にエピタキシャル層を堆積することで製造されます。このプロセスには、洗浄、酸化、フォトリソグラフィ、エッチング、フォトレジスト剥離、イオン注入、窒化シリコンの化学気相成長、研磨、スパッタリング、そしてその後の処理工程を経て、SiC単結晶基板上にデバイス構造を形成します。SiCパワーデバイスの主な種類には、SiCダイオード、SiCトランジスタ、SiCパワーモジュールなどがあります。上流工程の材料生産速度の遅さや歩留まりの低さなどの要因により、シリコンカーバイドデバイスの製造コストは比較的高くなっています。

さらに、シリコンカーバイドデバイスの製造には、次のような技術的な困難があります。

1) シリコンカーバイド材料の特性に適合した特定のプロセスを開発する必要があります。例えば、SiCは融点が高いため、従来の熱拡散法は効果がありません。イオン注入ドーピング法を用い、温度、加熱速度、加熱時間、ガス流量などのパラメータを正確に制御する必要があります。SiCは化学溶剤に対して不活性です。ドライエッチングなどの手法を用い、マスク材料、ガス混合比、側壁傾斜の制御、エッチング速度、側壁粗さなどを最適化・開発する必要があります。

2) シリコンカーバイドウェハ上に金属電極を製造するには、10-5Ω²以下の接触抵抗が求められます。この要件を満たす電極材料であるNiとAlは100℃を超えると熱安定性が低下しますが、Al/Niはより優れた熱安定性を有します。/W/Au複合電極材料の接触抵抗は10-3Ω²高くなります。

3) SiC は切削摩耗が大きく、その硬度はダイヤモンドに次ぐため、切断、研削、研磨などの技術に高い要件が求められます。

さらに、トレンチ型シリコンカーバイドパワーデバイスは製造がより困難です。デバイス構造の違いにより、シリコンカーバイドパワーデバイスは主にプレーナ型デバイスとトレンチ型デバイスに分けられます。プレーナ型シリコンカーバイドパワーデバイスは、単位の一貫性が良く、製造プロセスが簡単ですが、JFET効果の影響を受けやすく、寄生容量とオン抵抗が大きくなります。プレーナ型デバイスと比較して、トレンチ型シリコンカーバイドパワーデバイスは単位の一貫性が低く、製造プロセスが複雑です。ただし、トレンチ構造はデバイス単位密度の向上に役立ち、JFET効果が発生しにくく、チャネル移動度の問題を解決するのに有利です。オン抵抗が小さく、寄生容量が小さく、スイッチングエネルギー消費が少ないなどの優れた特性を備えています。コストと性能の面で大きな利点があり、シリコンカーバイドパワーデバイスの開発の主流となっています。 Rohm の公式サイトによると、ROHM Gen3 構造 (Gen1 トレンチ構造) は Gen2 (Plannar2) のチップ面積のわずか 75% であり、同じチップサイズで ROHM Gen3 構造のオン抵抗は 50% 削減されています。

シリコンカーバイド基板、エピタキシー、フロントエンド、研究開発費などは、それぞれシリコンカーバイドデバイスの製造コストの47%、23%、19%、6%、5%を占めています。

最後に、シリコンカーバイド産業チェーンにおける基板の技術的障壁を打破することに焦点を当てます。

シリコンカーバイド基板の製造プロセスはシリコンベースの基板の製造プロセスと似ていますが、より困難です。

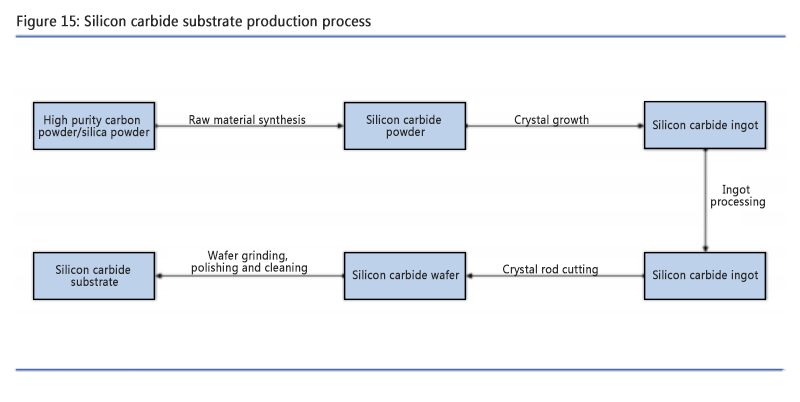

シリコンカーバイド基板の製造プロセスには、一般的に、原料の合成、結晶成長、インゴットの処理、インゴットの切断、ウェーハの研削、研磨、洗浄などの工程が含まれます。

結晶成長段階はプロセス全体の中核であり、このステップでシリコンカーバイド基板の電気特性が決まります。

炭化ケイ素材料は、通常の条件下では液相で成長させることが困難です。現在市場で普及している気相成長法では、成長温度が2300℃を超え、成長温度の精密な制御が必要です。操作プロセス全体を観察することはほとんど困難で、わずかな誤差が製品の廃棄につながります。比較すると、シリコン材料は1600℃しか必要とせず、これははるかに低いです。炭化ケイ素基板の準備も、結晶成長が遅いことと、高い結晶形状の要件などの困難に直面しています。炭化ケイ素ウェーハの成長には約7〜10日かかりますが、シリコンロッドの引き上げにはわずか2日半しかかかりません。さらに、炭化ケイ素はダイヤモンドに次ぐ硬度を持つ材料です。切断、研削、研磨中に損失が大きく、出力率はわずか60%です。

シリコンカーバイド基板のサイズは大型化傾向にあることは周知の事実です。サイズが拡大し続けるにつれて、直径拡大技術に対する要件はますます厳しくなっています。結晶の反復成長を実現するには、様々な技術制御要素を組み合わせる必要があります。

投稿日時: 2024年5月22日