ਤਿਕੋਣੀ ਨੁਕਸ

ਤਿਕੋਣੀ ਨੁਕਸ SiC ਐਪੀਟੈਕਸੀਅਲ ਪਰਤਾਂ ਵਿੱਚ ਸਭ ਤੋਂ ਘਾਤਕ ਰੂਪ ਵਿਗਿਆਨਿਕ ਨੁਕਸ ਹਨ। ਵੱਡੀ ਗਿਣਤੀ ਵਿੱਚ ਸਾਹਿਤ ਰਿਪੋਰਟਾਂ ਨੇ ਦਿਖਾਇਆ ਹੈ ਕਿ ਤਿਕੋਣੀ ਨੁਕਸ ਦਾ ਗਠਨ 3C ਕ੍ਰਿਸਟਲ ਰੂਪ ਨਾਲ ਸਬੰਧਤ ਹੈ। ਹਾਲਾਂਕਿ, ਵੱਖ-ਵੱਖ ਵਿਕਾਸ ਵਿਧੀਆਂ ਦੇ ਕਾਰਨ, ਐਪੀਟੈਕਸੀਅਲ ਪਰਤ ਦੀ ਸਤਹ 'ਤੇ ਬਹੁਤ ਸਾਰੇ ਤਿਕੋਣੀ ਨੁਕਸ ਦਾ ਰੂਪ ਵਿਗਿਆਨ ਕਾਫ਼ੀ ਵੱਖਰਾ ਹੈ। ਇਸਨੂੰ ਮੋਟੇ ਤੌਰ 'ਤੇ ਹੇਠ ਲਿਖੀਆਂ ਕਿਸਮਾਂ ਵਿੱਚ ਵੰਡਿਆ ਜਾ ਸਕਦਾ ਹੈ:

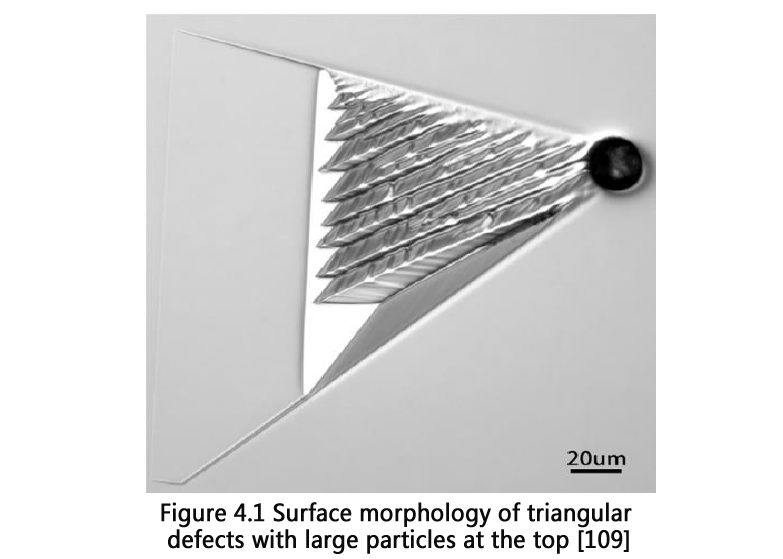

(1) ਉੱਪਰ ਵੱਡੇ ਕਣਾਂ ਵਾਲੇ ਤਿਕੋਣੀ ਨੁਕਸ ਹਨ।

ਇਸ ਕਿਸਮ ਦੇ ਤਿਕੋਣੀ ਨੁਕਸ ਦੇ ਉੱਪਰ ਇੱਕ ਵੱਡਾ ਗੋਲਾਕਾਰ ਕਣ ਹੁੰਦਾ ਹੈ, ਜੋ ਕਿ ਵਿਕਾਸ ਪ੍ਰਕਿਰਿਆ ਦੌਰਾਨ ਡਿੱਗਦੀਆਂ ਵਸਤੂਆਂ ਕਾਰਨ ਹੋ ਸਕਦਾ ਹੈ। ਇਸ ਸਿਖਰ ਤੋਂ ਹੇਠਾਂ ਵੱਲ ਇੱਕ ਖੁਰਦਰੀ ਸਤ੍ਹਾ ਵਾਲਾ ਇੱਕ ਛੋਟਾ ਤਿਕੋਣੀ ਖੇਤਰ ਦੇਖਿਆ ਜਾ ਸਕਦਾ ਹੈ। ਇਹ ਇਸ ਤੱਥ ਦੇ ਕਾਰਨ ਹੈ ਕਿ ਐਪੀਟੈਕਸੀਅਲ ਪ੍ਰਕਿਰਿਆ ਦੌਰਾਨ, ਤਿਕੋਣੀ ਖੇਤਰ ਵਿੱਚ ਦੋ ਵੱਖ-ਵੱਖ 3C-SiC ਪਰਤਾਂ ਲਗਾਤਾਰ ਬਣੀਆਂ ਹੁੰਦੀਆਂ ਹਨ, ਜਿਨ੍ਹਾਂ ਵਿੱਚੋਂ ਪਹਿਲੀ ਪਰਤ ਇੰਟਰਫੇਸ 'ਤੇ ਨਿਊਕਲੀਏਟ ਹੁੰਦੀ ਹੈ ਅਤੇ 4H-SiC ਸਟੈਪ ਫਲੋ ਦੁਆਰਾ ਵਧਦੀ ਹੈ। ਜਿਵੇਂ-ਜਿਵੇਂ ਐਪੀਟੈਕਸੀਅਲ ਪਰਤ ਦੀ ਮੋਟਾਈ ਵਧਦੀ ਹੈ, 3C ਪੌਲੀਟਾਈਪ ਦੀ ਦੂਜੀ ਪਰਤ ਨਿਊਕਲੀਏਟ ਹੁੰਦੀ ਹੈ ਅਤੇ ਛੋਟੇ ਤਿਕੋਣੀ ਟੋਇਆਂ ਵਿੱਚ ਵਧਦੀ ਹੈ, ਪਰ 4H ਵਿਕਾਸ ਕਦਮ 3C ਪੌਲੀਟਾਈਪ ਖੇਤਰ ਨੂੰ ਪੂਰੀ ਤਰ੍ਹਾਂ ਨਹੀਂ ਢੱਕਦਾ, ਜਿਸ ਨਾਲ 3C-SiC ਦਾ V-ਆਕਾਰ ਵਾਲਾ ਗਰੂਵ ਖੇਤਰ ਅਜੇ ਵੀ ਸਪੱਸ਼ਟ ਤੌਰ 'ਤੇ ਦਿਖਾਈ ਦਿੰਦਾ ਹੈ।

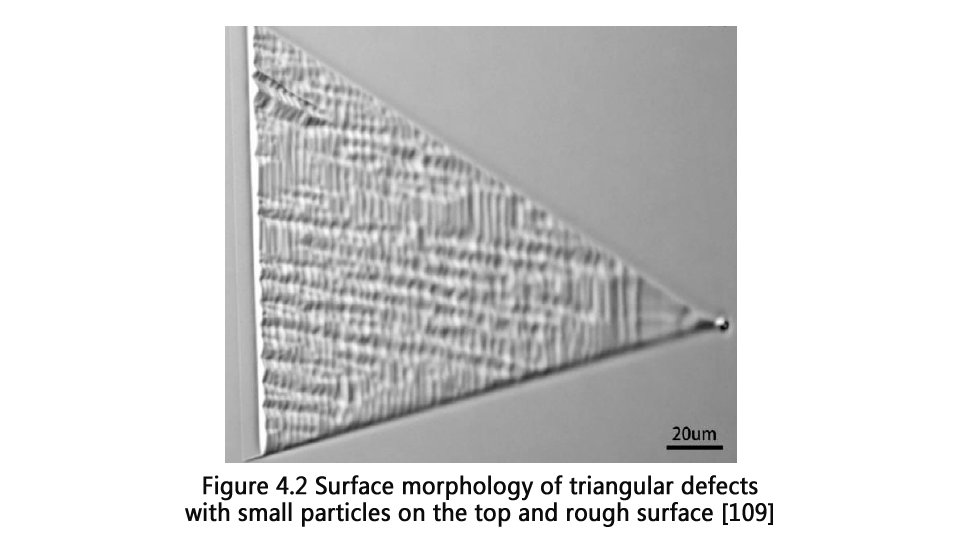

(2) ਉੱਪਰ ਛੋਟੇ ਕਣ ਹਨ ਅਤੇ ਖੁਰਦਰੀ ਸਤ੍ਹਾ ਦੇ ਨਾਲ ਤਿਕੋਣੀ ਨੁਕਸ ਹਨ।

ਇਸ ਕਿਸਮ ਦੇ ਤਿਕੋਣੀ ਨੁਕਸ ਦੇ ਸਿਖਰਾਂ 'ਤੇ ਕਣ ਬਹੁਤ ਛੋਟੇ ਹੁੰਦੇ ਹਨ, ਜਿਵੇਂ ਕਿ ਚਿੱਤਰ 4.2 ਵਿੱਚ ਦਿਖਾਇਆ ਗਿਆ ਹੈ। ਅਤੇ ਤਿਕੋਣੀ ਖੇਤਰ ਦਾ ਜ਼ਿਆਦਾਤਰ ਹਿੱਸਾ 4H-SiC ਦੇ ਸਟੈਪ ਫਲੋ ਦੁਆਰਾ ਢੱਕਿਆ ਹੋਇਆ ਹੈ, ਯਾਨੀ ਕਿ, ਪੂਰੀ 3C-SiC ਪਰਤ ਪੂਰੀ ਤਰ੍ਹਾਂ 4H-SiC ਪਰਤ ਦੇ ਹੇਠਾਂ ਏਮਬੈਡ ਕੀਤੀ ਗਈ ਹੈ। ਤਿਕੋਣੀ ਨੁਕਸ ਵਾਲੀ ਸਤ੍ਹਾ 'ਤੇ 4H-SiC ਦੇ ਸਿਰਫ ਵਾਧੇ ਦੇ ਪੜਾਅ ਹੀ ਦੇਖੇ ਜਾ ਸਕਦੇ ਹਨ, ਪਰ ਇਹ ਕਦਮ ਰਵਾਇਤੀ 4H ਕ੍ਰਿਸਟਲ ਵਾਧੇ ਦੇ ਕਦਮਾਂ ਨਾਲੋਂ ਬਹੁਤ ਵੱਡੇ ਹਨ।

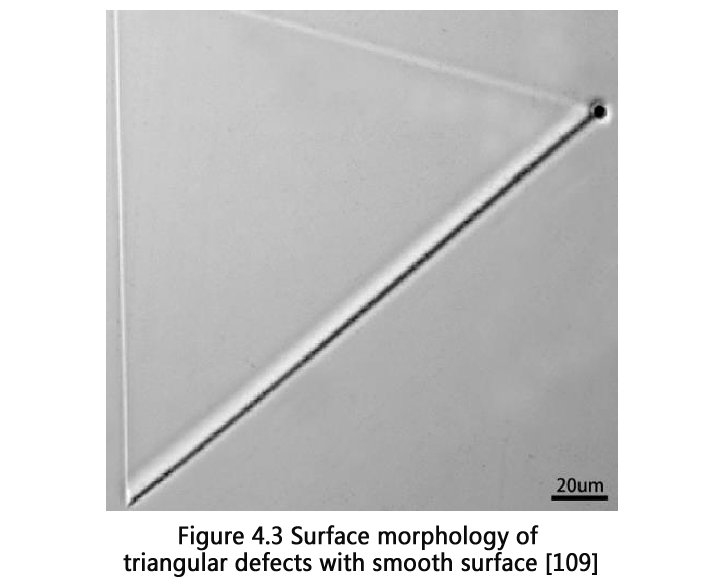

(3) ਨਿਰਵਿਘਨ ਸਤਹ ਦੇ ਨਾਲ ਤਿਕੋਣੀ ਨੁਕਸ

ਇਸ ਕਿਸਮ ਦੇ ਤਿਕੋਣੀ ਨੁਕਸ ਦੀ ਸਤ੍ਹਾ ਦੀ ਰੂਪ ਵਿਗਿਆਨ ਨਿਰਵਿਘਨ ਹੁੰਦੀ ਹੈ, ਜਿਵੇਂ ਕਿ ਚਿੱਤਰ 4.3 ਵਿੱਚ ਦਿਖਾਇਆ ਗਿਆ ਹੈ। ਅਜਿਹੇ ਤਿਕੋਣੀ ਨੁਕਸ ਲਈ, 3C-SiC ਪਰਤ 4H-SiC ਦੇ ਸਟੈਪ ਫਲੋ ਦੁਆਰਾ ਢੱਕੀ ਹੁੰਦੀ ਹੈ, ਅਤੇ ਸਤ੍ਹਾ 'ਤੇ 4H ਕ੍ਰਿਸਟਲ ਰੂਪ ਬਾਰੀਕ ਅਤੇ ਨਿਰਵਿਘਨ ਵਧਦਾ ਹੈ।

ਐਪੀਟੈਕਸੀਅਲ ਟੋਏ ਦੇ ਨੁਕਸ

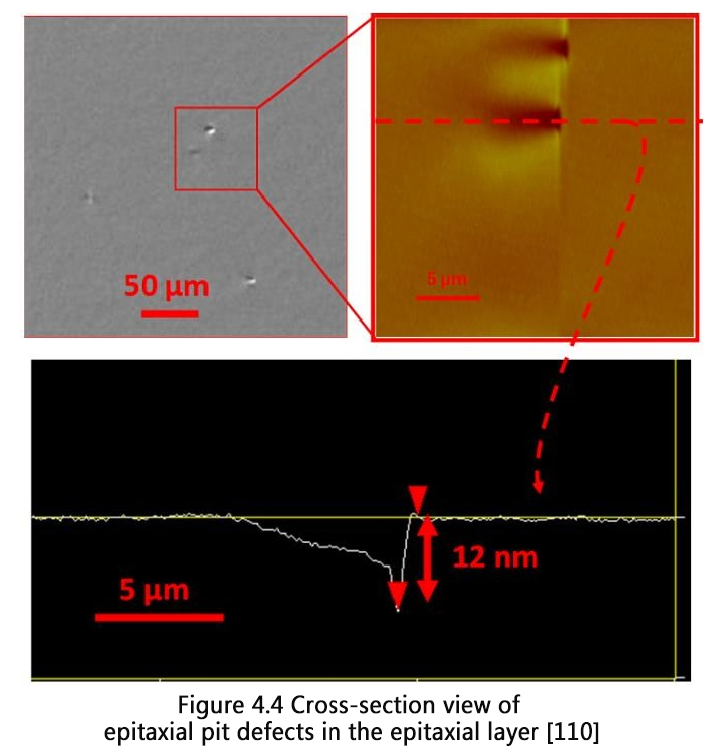

ਐਪੀਟੈਕਸੀਅਲ ਪਿਟਸ (ਪਿਟਸ) ਸਭ ਤੋਂ ਆਮ ਸਤਹ ਰੂਪ ਵਿਗਿਆਨ ਨੁਕਸਾਂ ਵਿੱਚੋਂ ਇੱਕ ਹਨ, ਅਤੇ ਉਹਨਾਂ ਦੀ ਖਾਸ ਸਤਹ ਰੂਪ ਵਿਗਿਆਨ ਅਤੇ ਢਾਂਚਾਗਤ ਰੂਪਰੇਖਾ ਚਿੱਤਰ 4.4 ਵਿੱਚ ਦਿਖਾਈ ਗਈ ਹੈ। ਡਿਵਾਈਸ ਦੇ ਪਿਛਲੇ ਪਾਸੇ KOH ਐਚਿੰਗ ਤੋਂ ਬਾਅਦ ਦੇਖੇ ਗਏ ਥ੍ਰੈਡਿੰਗ ਡਿਸਲੋਕੇਸ਼ਨ (TD) ਖੋਰ ਵਾਲੇ ਟੋਇਆਂ ਦੀ ਸਥਿਤੀ ਡਿਵਾਈਸ ਦੀ ਤਿਆਰੀ ਤੋਂ ਪਹਿਲਾਂ ਐਪੀਟੈਕਸੀਅਲ ਟੋਇਆਂ ਦੀ ਸਥਿਤੀ ਨਾਲ ਸਪਸ਼ਟ ਮੇਲ ਖਾਂਦੀ ਹੈ, ਜੋ ਦਰਸਾਉਂਦੀ ਹੈ ਕਿ ਐਪੀਟੈਕਸੀਅਲ ਟੋਇਆਂ ਦੇ ਨੁਕਸਾਂ ਦਾ ਗਠਨ ਥ੍ਰੈਡਿੰਗ ਡਿਸਲੋਕੇਸ਼ਨ ਨਾਲ ਸਬੰਧਤ ਹੈ।

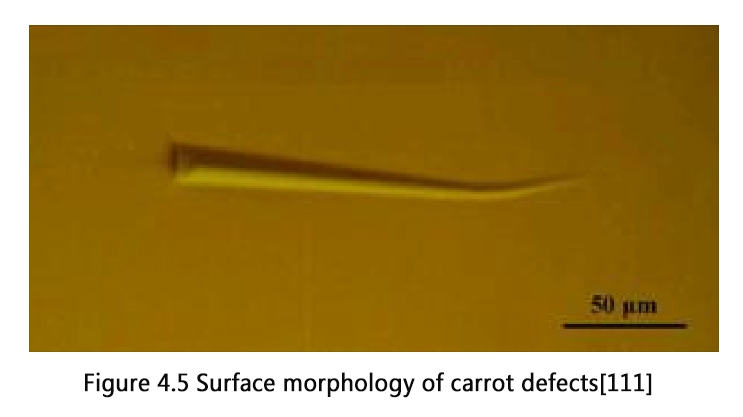

ਗਾਜਰ ਦੇ ਨੁਕਸ

ਗਾਜਰ ਦੇ ਨੁਕਸ 4H-SiC ਐਪੀਟੈਕਸੀਅਲ ਪਰਤਾਂ ਵਿੱਚ ਇੱਕ ਆਮ ਸਤਹ ਨੁਕਸ ਹਨ, ਅਤੇ ਉਹਨਾਂ ਦੀ ਖਾਸ ਰੂਪ ਵਿਗਿਆਨ ਚਿੱਤਰ 4.5 ਵਿੱਚ ਦਿਖਾਈ ਗਈ ਹੈ। ਗਾਜਰ ਦੇ ਨੁਕਸ ਨੂੰ ਸਟੈਪ-ਵਰਗੇ ਡਿਸਲੋਕੇਸ਼ਨ ਦੁਆਰਾ ਜੁੜੇ ਬੇਸਲ ਪਲੇਨ 'ਤੇ ਸਥਿਤ ਫ੍ਰੈਂਕੋਨੀਅਨ ਅਤੇ ਪ੍ਰਿਜ਼ਮੈਟਿਕ ਸਟੈਕਿੰਗ ਫਾਲਟ ਦੇ ਇੰਟਰਸੈਕਸ਼ਨ ਦੁਆਰਾ ਬਣਾਇਆ ਗਿਆ ਦੱਸਿਆ ਗਿਆ ਹੈ। ਇਹ ਵੀ ਰਿਪੋਰਟ ਕੀਤਾ ਗਿਆ ਹੈ ਕਿ ਗਾਜਰ ਦੇ ਨੁਕਸ ਦਾ ਗਠਨ ਸਬਸਟਰੇਟ ਵਿੱਚ TSD ਨਾਲ ਸਬੰਧਤ ਹੈ। ਸੁਚੀਦਾ ਐਚ. ਐਟ ਅਲ. ਨੇ ਪਾਇਆ ਕਿ ਐਪੀਟੈਕਸੀਅਲ ਪਰਤ ਵਿੱਚ ਗਾਜਰ ਦੇ ਨੁਕਸ ਦੀ ਘਣਤਾ ਸਬਸਟਰੇਟ ਵਿੱਚ TSD ਦੀ ਘਣਤਾ ਦੇ ਅਨੁਪਾਤੀ ਹੈ। ਅਤੇ ਐਪੀਟੈਕਸੀਅਲ ਵਾਧੇ ਤੋਂ ਪਹਿਲਾਂ ਅਤੇ ਬਾਅਦ ਵਿੱਚ ਸਤਹ ਰੂਪ ਵਿਗਿਆਨ ਚਿੱਤਰਾਂ ਦੀ ਤੁਲਨਾ ਕਰਕੇ, ਸਾਰੇ ਦੇਖੇ ਗਏ ਗਾਜਰ ਦੇ ਨੁਕਸ ਸਬਸਟਰੇਟ ਵਿੱਚ TSD ਨਾਲ ਮੇਲ ਖਾਂਦੇ ਪਾਏ ਜਾ ਸਕਦੇ ਹਨ। ਵੂ ਐਚ. ਐਟ ਅਲ. ਨੇ ਰਮਨ ਸਕੈਟਰਿੰਗ ਟੈਸਟ ਵਿਸ਼ੇਸ਼ਤਾ ਦੀ ਵਰਤੋਂ ਇਹ ਪਤਾ ਲਗਾਉਣ ਲਈ ਕੀਤੀ ਕਿ ਗਾਜਰ ਦੇ ਨੁਕਸ ਵਿੱਚ 3C ਕ੍ਰਿਸਟਲ ਰੂਪ ਨਹੀਂ ਸੀ, ਪਰ ਸਿਰਫ 4H-SiC ਪੌਲੀਟਾਈਪ ਸੀ।

MOSFET ਡਿਵਾਈਸ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ 'ਤੇ ਤਿਕੋਣੀ ਨੁਕਸਾਂ ਦਾ ਪ੍ਰਭਾਵ

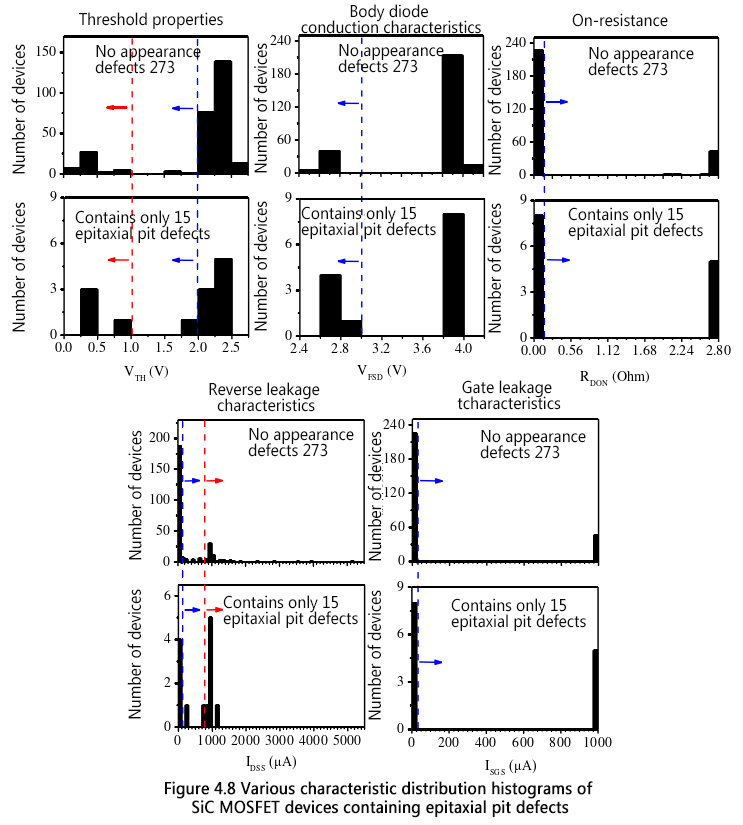

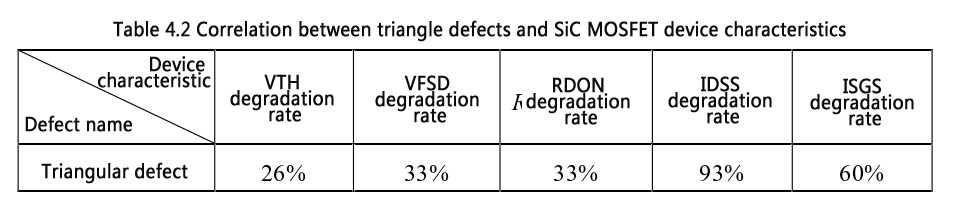

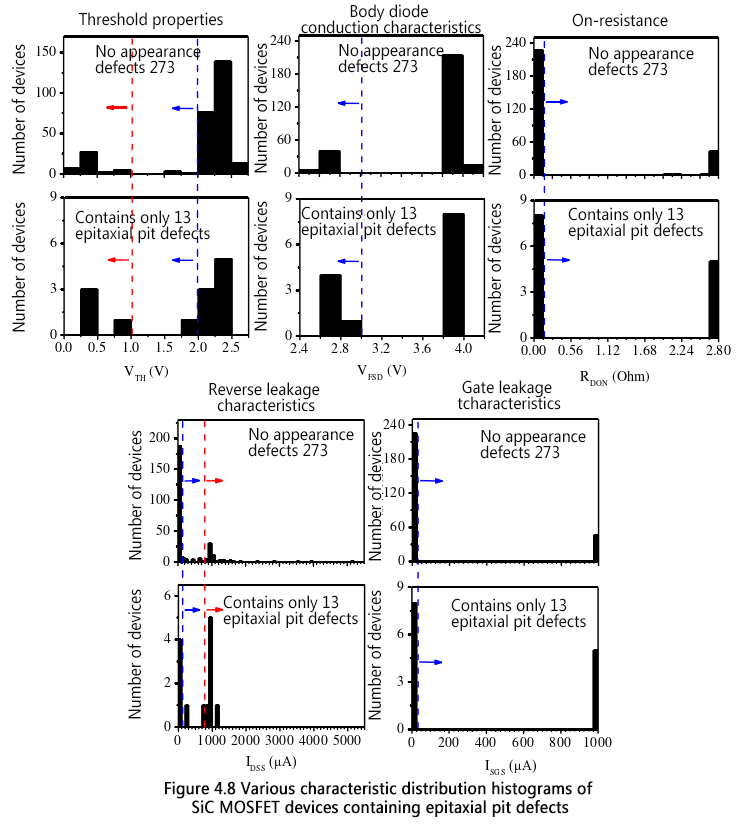

ਚਿੱਤਰ 4.7 ਇੱਕ ਯੰਤਰ ਦੀਆਂ ਪੰਜ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ ਦੀ ਅੰਕੜਾ ਵੰਡ ਦਾ ਇੱਕ ਹਿਸਟੋਗ੍ਰਾਮ ਹੈ ਜਿਸ ਵਿੱਚ ਤਿਕੋਣੀ ਨੁਕਸ ਹਨ। ਨੀਲੀ ਬਿੰਦੀ ਵਾਲੀ ਲਾਈਨ ਡਿਵਾਈਸ ਵਿਸ਼ੇਸ਼ਤਾ ਦੇ ਨਿਘਾਰ ਲਈ ਵੰਡਣ ਵਾਲੀ ਲਾਈਨ ਹੈ, ਅਤੇ ਲਾਲ ਬਿੰਦੀ ਵਾਲੀ ਲਾਈਨ ਡਿਵਾਈਸ ਅਸਫਲਤਾ ਲਈ ਵੰਡਣ ਵਾਲੀ ਲਾਈਨ ਹੈ। ਯੰਤਰ ਅਸਫਲਤਾ ਲਈ, ਤਿਕੋਣੀ ਨੁਕਸ ਦਾ ਬਹੁਤ ਪ੍ਰਭਾਵ ਪੈਂਦਾ ਹੈ, ਅਤੇ ਅਸਫਲਤਾ ਦਰ 93% ਤੋਂ ਵੱਧ ਹੈ। ਇਹ ਮੁੱਖ ਤੌਰ 'ਤੇ ਯੰਤਰਾਂ ਦੀਆਂ ਰਿਵਰਸ ਲੀਕੇਜ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ 'ਤੇ ਤਿਕੋਣੀ ਨੁਕਸ ਦੇ ਪ੍ਰਭਾਵ ਨੂੰ ਮੰਨਿਆ ਜਾਂਦਾ ਹੈ। ਤਿਕੋਣੀ ਨੁਕਸ ਵਾਲੇ 93% ਤੱਕ ਯੰਤਰਾਂ ਵਿੱਚ ਰਿਵਰਸ ਲੀਕੇਜ ਵਿੱਚ ਕਾਫ਼ੀ ਵਾਧਾ ਹੋਇਆ ਹੈ। ਇਸ ਤੋਂ ਇਲਾਵਾ, ਤਿਕੋਣੀ ਨੁਕਸ ਦਾ ਗੇਟ ਲੀਕੇਜ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ 'ਤੇ ਵੀ ਗੰਭੀਰ ਪ੍ਰਭਾਵ ਪੈਂਦਾ ਹੈ, ਜਿਸਦੀ ਡਿਗ੍ਰੇਡੇਸ਼ਨ ਦਰ 60% ਹੈ। ਜਿਵੇਂ ਕਿ ਸਾਰਣੀ 4.2 ਵਿੱਚ ਦਿਖਾਇਆ ਗਿਆ ਹੈ, ਥ੍ਰੈਸ਼ਹੋਲਡ ਵੋਲਟੇਜ ਡਿਗ੍ਰੇਡੇਸ਼ਨ ਅਤੇ ਬਾਡੀ ਡਾਇਓਡ ਵਿਸ਼ੇਸ਼ਤਾ ਦੇ ਨਿਘਾਰ ਲਈ, ਤਿਕੋਣੀ ਨੁਕਸ ਦਾ ਪ੍ਰਭਾਵ ਛੋਟਾ ਹੈ, ਅਤੇ ਡਿਗ੍ਰੇਡੇਸ਼ਨ ਅਨੁਪਾਤ ਕ੍ਰਮਵਾਰ 26% ਅਤੇ 33% ਹੈ। ਔਨ-ਰੋਧ ਵਿੱਚ ਵਾਧਾ ਕਰਨ ਦੇ ਮਾਮਲੇ ਵਿੱਚ, ਤਿਕੋਣੀ ਨੁਕਸ ਦਾ ਪ੍ਰਭਾਵ ਕਮਜ਼ੋਰ ਹੈ, ਅਤੇ ਡਿਗ੍ਰੇਡੇਸ਼ਨ ਅਨੁਪਾਤ ਲਗਭਗ 33% ਹੈ।

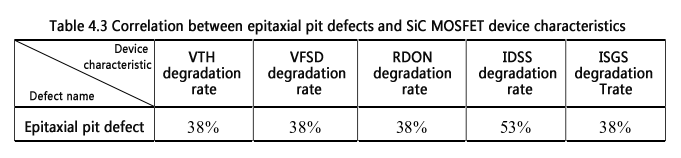

MOSFET ਡਿਵਾਈਸ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ 'ਤੇ ਐਪੀਟੈਕਸੀਅਲ ਪਿਟ ਨੁਕਸ ਦਾ ਪ੍ਰਭਾਵ

ਚਿੱਤਰ 4.8 ਐਪੀਟੈਕਸੀਅਲ ਪਿਟ ਡਿਫੈਕਟਸ ਵਾਲੇ ਡਿਵਾਈਸ ਦੀਆਂ ਪੰਜ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ ਦੀ ਅੰਕੜਾ ਵੰਡ ਦਾ ਇੱਕ ਹਿਸਟੋਗ੍ਰਾਮ ਹੈ। ਨੀਲੀ ਬਿੰਦੀ ਵਾਲੀ ਲਾਈਨ ਡਿਵਾਈਸ ਵਿਸ਼ੇਸ਼ਤਾ ਡਿਗਰੇਡੇਸ਼ਨ ਲਈ ਵੰਡਣ ਵਾਲੀ ਲਾਈਨ ਹੈ, ਅਤੇ ਲਾਲ ਬਿੰਦੀ ਵਾਲੀ ਲਾਈਨ ਡਿਵਾਈਸ ਫੇਲ੍ਹ ਹੋਣ ਲਈ ਵੰਡਣ ਵਾਲੀ ਲਾਈਨ ਹੈ। ਇਸ ਤੋਂ ਇਹ ਦੇਖਿਆ ਜਾ ਸਕਦਾ ਹੈ ਕਿ SiC MOSFET ਨਮੂਨੇ ਵਿੱਚ ਐਪੀਟੈਕਸੀਅਲ ਪਿਟ ਡਿਫੈਕਟਸ ਵਾਲੇ ਡਿਵਾਈਸਾਂ ਦੀ ਗਿਣਤੀ ਤਿਕੋਣੀ ਨੁਕਸ ਵਾਲੇ ਡਿਵਾਈਸਾਂ ਦੀ ਗਿਣਤੀ ਦੇ ਬਰਾਬਰ ਹੈ। ਡਿਵਾਈਸ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ 'ਤੇ ਐਪੀਟੈਕਸੀਅਲ ਪਿਟ ਡਿਫੈਕਟਸ ਦਾ ਪ੍ਰਭਾਵ ਤਿਕੋਣੀ ਨੁਕਸ ਤੋਂ ਵੱਖਰਾ ਹੈ। ਡਿਵਾਈਸ ਅਸਫਲਤਾ ਦੇ ਮਾਮਲੇ ਵਿੱਚ, ਐਪੀਟੈਕਸੀਅਲ ਪਿਟ ਡਿਫੈਕਟਸ ਵਾਲੇ ਡਿਵਾਈਸਾਂ ਦੀ ਅਸਫਲਤਾ ਦਰ ਸਿਰਫ 47% ਹੈ। ਤਿਕੋਣੀ ਨੁਕਸ ਦੇ ਮੁਕਾਬਲੇ, ਡਿਵਾਈਸ ਦੇ ਰਿਵਰਸ ਲੀਕੇਜ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ ਅਤੇ ਗੇਟ ਲੀਕੇਜ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ 'ਤੇ ਐਪੀਟੈਕਸੀਅਲ ਪਿਟ ਡਿਫੈਕਟਸ ਦਾ ਪ੍ਰਭਾਵ ਕਾਫ਼ੀ ਕਮਜ਼ੋਰ ਹੋ ਗਿਆ ਹੈ, ਜਿਵੇਂ ਕਿ ਸਾਰਣੀ 4.3 ਵਿੱਚ ਦਿਖਾਇਆ ਗਿਆ ਹੈ, ਕ੍ਰਮਵਾਰ 53% ਅਤੇ 38% ਦੇ ਡਿਗਰੇਡੇਸ਼ਨ ਅਨੁਪਾਤ ਦੇ ਨਾਲ। ਦੂਜੇ ਪਾਸੇ, ਥ੍ਰੈਸ਼ਹੋਲਡ ਵੋਲਟੇਜ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ, ਬਾਡੀ ਡਾਇਓਡ ਕੰਡਕਸ਼ਨ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ ਅਤੇ ਔਨ-ਰੋਧ 'ਤੇ ਐਪੀਟੈਕਸੀਅਲ ਪਿਟ ਡਿਫੈਕਟਸ ਦਾ ਪ੍ਰਭਾਵ ਤਿਕੋਣੀ ਨੁਕਸ ਨਾਲੋਂ ਵੱਧ ਹੈ, ਡਿਗਰੇਡੇਸ਼ਨ ਅਨੁਪਾਤ 38% ਤੱਕ ਪਹੁੰਚਦਾ ਹੈ।

ਆਮ ਤੌਰ 'ਤੇ, ਦੋ ਰੂਪ ਵਿਗਿਆਨਿਕ ਨੁਕਸ, ਅਰਥਾਤ ਤਿਕੋਣ ਅਤੇ ਐਪੀਟੈਕਸੀਅਲ ਪਿਟਸ, SiC MOSFET ਡਿਵਾਈਸਾਂ ਦੀ ਅਸਫਲਤਾ ਅਤੇ ਵਿਸ਼ੇਸ਼ਤਾ ਦੇ ਵਿਗਾੜ 'ਤੇ ਮਹੱਤਵਪੂਰਨ ਪ੍ਰਭਾਵ ਪਾਉਂਦੇ ਹਨ। ਤਿਕੋਣੀ ਨੁਕਸ ਦੀ ਮੌਜੂਦਗੀ ਸਭ ਤੋਂ ਘਾਤਕ ਹੈ, ਜਿਸਦੀ ਅਸਫਲਤਾ ਦਰ 93% ਤੱਕ ਉੱਚੀ ਹੈ, ਜੋ ਮੁੱਖ ਤੌਰ 'ਤੇ ਡਿਵਾਈਸ ਦੇ ਰਿਵਰਸ ਲੀਕੇਜ ਵਿੱਚ ਇੱਕ ਮਹੱਤਵਪੂਰਨ ਵਾਧੇ ਵਜੋਂ ਪ੍ਰਗਟ ਹੁੰਦੀ ਹੈ। ਐਪੀਟੈਕਸੀਅਲ ਪਿਟ ਡਿਫੈਕਟਸ ਵਾਲੇ ਡਿਵਾਈਸਾਂ ਦੀ ਅਸਫਲਤਾ ਦਰ 47% ਘੱਟ ਸੀ। ਹਾਲਾਂਕਿ, ਐਪੀਟੈਕਸੀਅਲ ਪਿਟ ਡਿਫੈਕਟਸ ਦਾ ਡਿਵਾਈਸ ਦੇ ਥ੍ਰੈਸ਼ਹੋਲਡ ਵੋਲਟੇਜ, ਬਾਡੀ ਡਾਇਓਡ ਕੰਡਕਸ਼ਨ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ ਅਤੇ ਔਨ-ਰੋਧ 'ਤੇ ਤਿਕੋਣੀ ਨੁਕਸ ਨਾਲੋਂ ਜ਼ਿਆਦਾ ਪ੍ਰਭਾਵ ਪੈਂਦਾ ਹੈ।

ਪੋਸਟ ਸਮਾਂ: ਅਪ੍ਰੈਲ-16-2024