CVD SiC ਕੋਟਿੰਗ ਕੀ ਹੈ?

ਰਸਾਇਣਕ ਭਾਫ਼ ਜਮ੍ਹਾਂ (CVD) ਇੱਕ ਵੈਕਿਊਮ ਜਮ੍ਹਾਂ ਪ੍ਰਕਿਰਿਆ ਹੈ ਜੋ ਉੱਚ-ਸ਼ੁੱਧਤਾ ਵਾਲੇ ਠੋਸ ਪਦਾਰਥ ਪੈਦਾ ਕਰਨ ਲਈ ਵਰਤੀ ਜਾਂਦੀ ਹੈ। ਇਹ ਪ੍ਰਕਿਰਿਆ ਅਕਸਰ ਸੈਮੀਕੰਡਕਟਰ ਨਿਰਮਾਣ ਖੇਤਰ ਵਿੱਚ ਵੇਫਰਾਂ ਦੀ ਸਤ੍ਹਾ 'ਤੇ ਪਤਲੀਆਂ ਫਿਲਮਾਂ ਬਣਾਉਣ ਲਈ ਵਰਤੀ ਜਾਂਦੀ ਹੈ। CVD ਦੁਆਰਾ ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ ਤਿਆਰ ਕਰਨ ਦੀ ਪ੍ਰਕਿਰਿਆ ਵਿੱਚ, ਸਬਸਟਰੇਟ ਇੱਕ ਜਾਂ ਇੱਕ ਤੋਂ ਵੱਧ ਅਸਥਿਰ ਪੂਰਵਜਾਂ ਦੇ ਸੰਪਰਕ ਵਿੱਚ ਆਉਂਦਾ ਹੈ, ਜੋ ਲੋੜੀਂਦੇ ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ ਜਮ੍ਹਾਂ ਨੂੰ ਜਮ੍ਹਾਂ ਕਰਨ ਲਈ ਸਬਸਟਰੇਟ ਦੀ ਸਤ੍ਹਾ 'ਤੇ ਰਸਾਇਣਕ ਤੌਰ 'ਤੇ ਪ੍ਰਤੀਕਿਰਿਆ ਕਰਦੇ ਹਨ। ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ ਸਮੱਗਰੀ ਤਿਆਰ ਕਰਨ ਦੇ ਬਹੁਤ ਸਾਰੇ ਤਰੀਕਿਆਂ ਵਿੱਚੋਂ, ਰਸਾਇਣਕ ਭਾਫ਼ ਜਮ੍ਹਾਂ ਦੁਆਰਾ ਤਿਆਰ ਕੀਤੇ ਉਤਪਾਦਾਂ ਵਿੱਚ ਵਧੇਰੇ ਇਕਸਾਰਤਾ ਅਤੇ ਸ਼ੁੱਧਤਾ ਹੁੰਦੀ ਹੈ, ਅਤੇ ਇਸ ਵਿਧੀ ਵਿੱਚ ਮਜ਼ਬੂਤ ਪ੍ਰਕਿਰਿਆ ਨਿਯੰਤਰਣਯੋਗਤਾ ਹੁੰਦੀ ਹੈ। ਸੀਵੀਡੀ ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ ਸਮੱਗਰੀਆਂ ਵਿੱਚ ਸ਼ਾਨਦਾਰ ਥਰਮਲ, ਇਲੈਕਟ੍ਰੀਕਲ ਅਤੇ ਰਸਾਇਣਕ ਗੁਣਾਂ ਦਾ ਇੱਕ ਵਿਲੱਖਣ ਸੁਮੇਲ ਹੁੰਦਾ ਹੈ, ਜੋ ਉਹਨਾਂ ਨੂੰ ਸੈਮੀਕੰਡਕਟਰ ਉਦਯੋਗ ਵਿੱਚ ਵਰਤੋਂ ਲਈ ਬਹੁਤ ਢੁਕਵਾਂ ਬਣਾਉਂਦਾ ਹੈ ਜਿੱਥੇ ਉੱਚ-ਪ੍ਰਦਰਸ਼ਨ ਵਾਲੀਆਂ ਸਮੱਗਰੀਆਂ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ। ਸੀਵੀਡੀ ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ ਹਿੱਸੇ ਐਚਿੰਗ ਉਪਕਰਣ, ਐਮਓਸੀਵੀਡੀ ਉਪਕਰਣ, ਸੀ ਐਪੀਟੈਕਸੀਅਲ ਉਪਕਰਣ ਅਤੇ ਸੀਆਈਸੀ ਐਪੀਟੈਕਸੀਅਲ ਉਪਕਰਣ, ਤੇਜ਼ ਥਰਮਲ ਪ੍ਰੋਸੈਸਿੰਗ ਉਪਕਰਣ ਅਤੇ ਹੋਰ ਖੇਤਰਾਂ ਵਿੱਚ ਵਿਆਪਕ ਤੌਰ 'ਤੇ ਵਰਤੇ ਜਾਂਦੇ ਹਨ।

ਇਹ ਲੇਖ ਤਿਆਰ ਕਰਨ ਦੌਰਾਨ ਵੱਖ-ਵੱਖ ਪ੍ਰਕਿਰਿਆ ਤਾਪਮਾਨਾਂ 'ਤੇ ਉਗਾਈਆਂ ਗਈਆਂ ਪਤਲੀਆਂ ਫਿਲਮਾਂ ਦੀ ਗੁਣਵੱਤਾ ਦਾ ਵਿਸ਼ਲੇਸ਼ਣ ਕਰਨ 'ਤੇ ਕੇਂਦ੍ਰਿਤ ਹੈ।CVD SiC ਕੋਟਿੰਗ, ਤਾਂ ਜੋ ਸਭ ਤੋਂ ਢੁਕਵੇਂ ਪ੍ਰਕਿਰਿਆ ਤਾਪਮਾਨ ਦੀ ਚੋਣ ਕੀਤੀ ਜਾ ਸਕੇ। ਪ੍ਰਯੋਗ ਵਿੱਚ ਗ੍ਰੇਫਾਈਟ ਨੂੰ ਸਬਸਟਰੇਟ ਵਜੋਂ ਅਤੇ ਟ੍ਰਾਈਕਲੋਰੋਮਿਥਾਈਲਸਿਲੇਨ (MTS) ਨੂੰ ਪ੍ਰਤੀਕ੍ਰਿਆ ਸਰੋਤ ਗੈਸ ਵਜੋਂ ਵਰਤਿਆ ਜਾਂਦਾ ਹੈ। SiC ਕੋਟਿੰਗ ਘੱਟ-ਦਬਾਅ ਵਾਲੀ CVD ਪ੍ਰਕਿਰਿਆ ਦੁਆਰਾ ਜਮ੍ਹਾ ਕੀਤੀ ਜਾਂਦੀ ਹੈ, ਅਤੇ ਮਾਈਕ੍ਰੋਮੋਰਫੋਲੋਜੀCVD SiC ਕੋਟਿੰਗਇਸਦੀ ਸੰਰਚਨਾਤਮਕ ਘਣਤਾ ਦਾ ਵਿਸ਼ਲੇਸ਼ਣ ਕਰਨ ਲਈ ਇਲੈਕਟ੍ਰੌਨ ਮਾਈਕ੍ਰੋਸਕੋਪੀ ਨੂੰ ਸਕੈਨ ਕਰਕੇ ਦੇਖਿਆ ਜਾਂਦਾ ਹੈ।

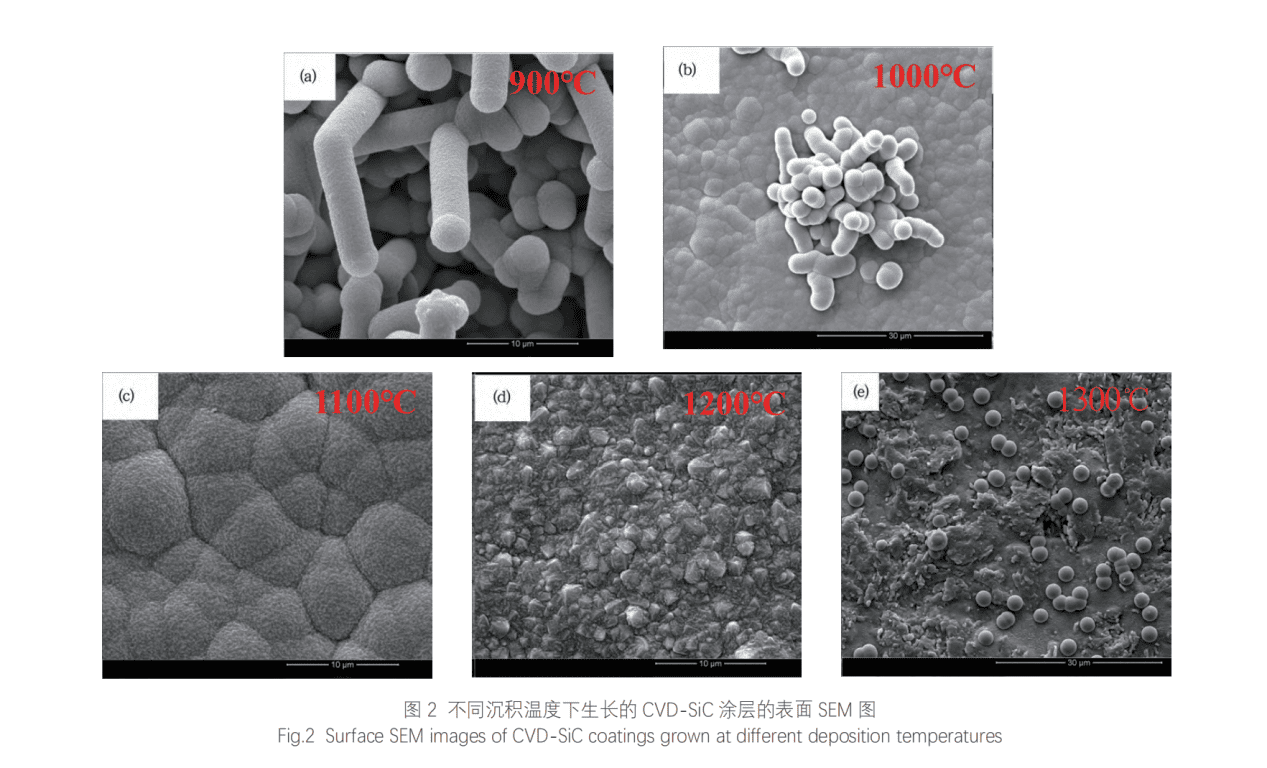

ਕਿਉਂਕਿ ਗ੍ਰਾਫਾਈਟ ਸਬਸਟਰੇਟ ਦਾ ਸਤ੍ਹਾ ਤਾਪਮਾਨ ਬਹੁਤ ਜ਼ਿਆਦਾ ਹੁੰਦਾ ਹੈ, ਇਸ ਲਈ ਵਿਚਕਾਰਲੀ ਗੈਸ ਨੂੰ ਸਬਸਟਰੇਟ ਸਤ੍ਹਾ ਤੋਂ ਸੋਖ ਲਿਆ ਜਾਵੇਗਾ ਅਤੇ ਡਿਸਚਾਰਜ ਕੀਤਾ ਜਾਵੇਗਾ, ਅਤੇ ਅੰਤ ਵਿੱਚ ਸਬਸਟਰੇਟ ਸਤ੍ਹਾ 'ਤੇ ਬਚੇ C ਅਤੇ Si ਠੋਸ ਪੜਾਅ SiC ਬਣਾ ਕੇ SiC ਕੋਟਿੰਗ ਬਣਾਉਣਗੇ। ਉਪਰੋਕਤ CVD-SiC ਵਿਕਾਸ ਪ੍ਰਕਿਰਿਆ ਦੇ ਅਨੁਸਾਰ, ਇਹ ਦੇਖਿਆ ਜਾ ਸਕਦਾ ਹੈ ਕਿ ਤਾਪਮਾਨ ਗੈਸ ਦੇ ਫੈਲਾਅ, MTS ਦੇ ਸੜਨ, ਬੂੰਦਾਂ ਦੇ ਗਠਨ ਅਤੇ ਵਿਚਕਾਰਲੀ ਗੈਸ ਦੇ ਡੀਸੋਰਪਸ਼ਨ ਅਤੇ ਡਿਸਚਾਰਜ ਨੂੰ ਪ੍ਰਭਾਵਤ ਕਰੇਗਾ, ਇਸ ਲਈ ਜਮ੍ਹਾ ਤਾਪਮਾਨ SiC ਕੋਟਿੰਗ ਦੇ ਰੂਪ ਵਿਗਿਆਨ ਵਿੱਚ ਇੱਕ ਮੁੱਖ ਭੂਮਿਕਾ ਨਿਭਾਏਗਾ। ਕੋਟਿੰਗ ਦਾ ਸੂਖਮ ਰੂਪ ਵਿਗਿਆਨ ਕੋਟਿੰਗ ਦੀ ਘਣਤਾ ਦਾ ਸਭ ਤੋਂ ਅਨੁਭਵੀ ਪ੍ਰਗਟਾਵਾ ਹੈ। ਇਸ ਲਈ, CVD SiC ਕੋਟਿੰਗ ਦੇ ਸੂਖਮ ਰੂਪ ਵਿਗਿਆਨ 'ਤੇ ਵੱਖ-ਵੱਖ ਜਮ੍ਹਾ ਤਾਪਮਾਨਾਂ ਦੇ ਪ੍ਰਭਾਵ ਦਾ ਅਧਿਐਨ ਕਰਨਾ ਜ਼ਰੂਰੀ ਹੈ। ਕਿਉਂਕਿ MTS 900~1600℃ ਦੇ ਵਿਚਕਾਰ SiC ਕੋਟਿੰਗ ਨੂੰ ਸੜ ਸਕਦਾ ਹੈ ਅਤੇ ਜਮ੍ਹਾ ਕਰ ਸਕਦਾ ਹੈ, ਇਸ ਲਈ ਇਹ ਪ੍ਰਯੋਗ CVD-SiC ਕੋਟਿੰਗ 'ਤੇ ਤਾਪਮਾਨ ਦੇ ਪ੍ਰਭਾਵ ਦਾ ਅਧਿਐਨ ਕਰਨ ਲਈ SiC ਕੋਟਿੰਗ ਦੀ ਤਿਆਰੀ ਲਈ 900℃, 1000℃, 1100℃, 1200℃ ਅਤੇ 1300℃ ਦੇ ਪੰਜ ਜਮ੍ਹਾ ਤਾਪਮਾਨਾਂ ਦੀ ਚੋਣ ਕਰਦਾ ਹੈ। ਖਾਸ ਮਾਪਦੰਡ ਸਾਰਣੀ 3 ਵਿੱਚ ਦਿਖਾਏ ਗਏ ਹਨ। ਚਿੱਤਰ 2 ਵੱਖ-ਵੱਖ ਜਮ੍ਹਾ ਤਾਪਮਾਨਾਂ 'ਤੇ ਉਗਾਏ ਗਏ CVD-SiC ਕੋਟਿੰਗ ਦੇ ਸੂਖਮ ਰੂਪ ਵਿਗਿਆਨ ਨੂੰ ਦਰਸਾਉਂਦਾ ਹੈ।

ਜਦੋਂ ਜਮ੍ਹਾ ਕਰਨ ਦਾ ਤਾਪਮਾਨ 900℃ ਹੁੰਦਾ ਹੈ, ਤਾਂ ਸਾਰਾ SiC ਫਾਈਬਰ ਆਕਾਰਾਂ ਵਿੱਚ ਵਧਦਾ ਹੈ। ਇਹ ਦੇਖਿਆ ਜਾ ਸਕਦਾ ਹੈ ਕਿ ਇੱਕ ਸਿੰਗਲ ਫਾਈਬਰ ਦਾ ਵਿਆਸ ਲਗਭਗ 3.5μm ਹੁੰਦਾ ਹੈ, ਅਤੇ ਇਸਦਾ ਆਕਾਰ ਅਨੁਪਾਤ ਲਗਭਗ 3 (<10) ਹੁੰਦਾ ਹੈ। ਇਸ ਤੋਂ ਇਲਾਵਾ, ਇਹ ਅਣਗਿਣਤ ਨੈਨੋ-SiC ਕਣਾਂ ਤੋਂ ਬਣਿਆ ਹੁੰਦਾ ਹੈ, ਇਸ ਲਈ ਇਹ ਇੱਕ ਪੌਲੀਕ੍ਰਿਸਟਲਾਈਨ SiC ਬਣਤਰ ਨਾਲ ਸਬੰਧਤ ਹੈ, ਜੋ ਕਿ ਰਵਾਇਤੀ SiC ਨੈਨੋਵਾਇਰਸ ਅਤੇ ਸਿੰਗਲ-ਕ੍ਰਿਸਟਲ SiC ਵਿਸਕਰਾਂ ਤੋਂ ਵੱਖਰਾ ਹੈ। ਇਹ ਰੇਸ਼ੇਦਾਰ SiC ਇੱਕ ਢਾਂਚਾਗਤ ਨੁਕਸ ਹੈ ਜੋ ਗੈਰ-ਵਾਜਬ ਪ੍ਰਕਿਰਿਆ ਮਾਪਦੰਡਾਂ ਕਾਰਨ ਹੁੰਦਾ ਹੈ। ਇਹ ਦੇਖਿਆ ਜਾ ਸਕਦਾ ਹੈ ਕਿ ਇਸ SiC ਕੋਟਿੰਗ ਦੀ ਬਣਤਰ ਮੁਕਾਬਲਤਨ ਢਿੱਲੀ ਹੈ, ਅਤੇ ਰੇਸ਼ੇਦਾਰ SiC ਦੇ ਵਿਚਕਾਰ ਵੱਡੀ ਗਿਣਤੀ ਵਿੱਚ ਪੋਰ ਹਨ, ਅਤੇ ਘਣਤਾ ਬਹੁਤ ਘੱਟ ਹੈ। ਇਸ ਲਈ, ਇਹ ਤਾਪਮਾਨ ਸੰਘਣੇ SiC ਕੋਟਿੰਗਾਂ ਦੀ ਤਿਆਰੀ ਲਈ ਢੁਕਵਾਂ ਨਹੀਂ ਹੈ। ਆਮ ਤੌਰ 'ਤੇ, ਰੇਸ਼ੇਦਾਰ SiC ਢਾਂਚਾਗਤ ਨੁਕਸ ਬਹੁਤ ਘੱਟ ਜਮ੍ਹਾ ਕਰਨ ਵਾਲੇ ਤਾਪਮਾਨ ਕਾਰਨ ਹੁੰਦੇ ਹਨ। ਘੱਟ ਤਾਪਮਾਨਾਂ 'ਤੇ, ਸਬਸਟਰੇਟ ਦੀ ਸਤ੍ਹਾ 'ਤੇ ਸੋਖੇ ਗਏ ਛੋਟੇ ਅਣੂਆਂ ਵਿੱਚ ਘੱਟ ਊਰਜਾ ਅਤੇ ਮਾੜੀ ਮਾਈਗ੍ਰੇਸ਼ਨ ਸਮਰੱਥਾ ਹੁੰਦੀ ਹੈ। ਇਸ ਲਈ, ਛੋਟੇ ਅਣੂ ਮਾਈਗ੍ਰੇਟ ਕਰਦੇ ਹਨ ਅਤੇ SiC ਅਨਾਜਾਂ (ਜਿਵੇਂ ਕਿ ਅਨਾਜ ਦੀ ਨੋਕ) ਦੀ ਸਭ ਤੋਂ ਘੱਟ ਸਤਹ ਮੁਕਤ ਊਰਜਾ ਤੱਕ ਵਧਦੇ ਹਨ। ਨਿਰੰਤਰ ਦਿਸ਼ਾਤਮਕ ਵਾਧਾ ਅੰਤ ਵਿੱਚ ਰੇਸ਼ੇਦਾਰ SiC ਢਾਂਚਾਗਤ ਨੁਕਸ ਬਣਾਉਂਦਾ ਹੈ।

CVD SiC ਕੋਟਿੰਗ ਦੀ ਤਿਆਰੀ:

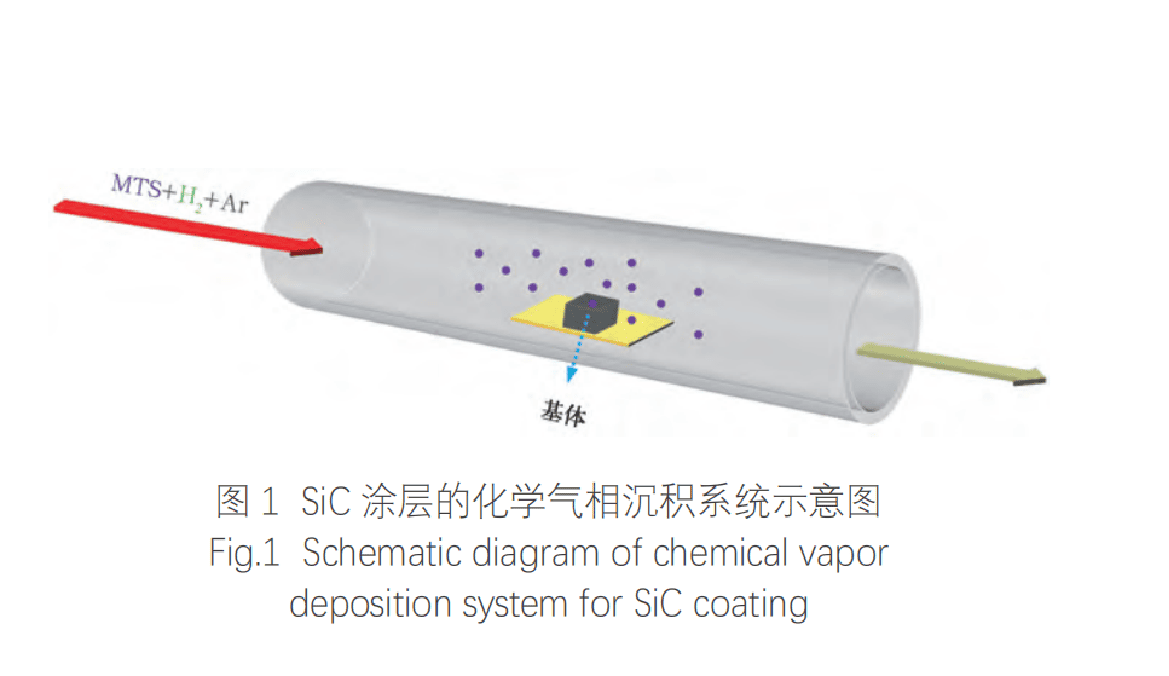

ਪਹਿਲਾਂ, ਗ੍ਰਾਫਾਈਟ ਸਬਸਟਰੇਟ ਨੂੰ ਇੱਕ ਉੱਚ-ਤਾਪਮਾਨ ਵੈਕਿਊਮ ਭੱਠੀ ਵਿੱਚ ਰੱਖਿਆ ਜਾਂਦਾ ਹੈ ਅਤੇ ਸੁਆਹ ਹਟਾਉਣ ਲਈ ਇੱਕ Ar ਵਾਯੂਮੰਡਲ ਵਿੱਚ 1 ਘੰਟੇ ਲਈ 1500℃ 'ਤੇ ਰੱਖਿਆ ਜਾਂਦਾ ਹੈ। ਫਿਰ ਗ੍ਰਾਫਾਈਟ ਬਲਾਕ ਨੂੰ 15x15x5mm ਦੇ ਇੱਕ ਬਲਾਕ ਵਿੱਚ ਕੱਟਿਆ ਜਾਂਦਾ ਹੈ, ਅਤੇ ਗ੍ਰਾਫਾਈਟ ਬਲਾਕ ਦੀ ਸਤ੍ਹਾ ਨੂੰ 1200-ਜਾਲੀ ਵਾਲੇ ਸੈਂਡਪੇਪਰ ਨਾਲ ਪਾਲਿਸ਼ ਕੀਤਾ ਜਾਂਦਾ ਹੈ ਤਾਂ ਜੋ ਸਤਹ ਦੇ ਛੇਦ ਖਤਮ ਕੀਤੇ ਜਾ ਸਕਣ ਜੋ SiC ਦੇ ਜਮ੍ਹਾਂ ਹੋਣ ਨੂੰ ਪ੍ਰਭਾਵਤ ਕਰਦੇ ਹਨ। ਇਲਾਜ ਕੀਤੇ ਗ੍ਰਾਫਾਈਟ ਬਲਾਕ ਨੂੰ ਐਨਹਾਈਡ੍ਰਸ ਈਥਾਨੌਲ ਅਤੇ ਡਿਸਟਿਲਡ ਪਾਣੀ ਨਾਲ ਧੋਤਾ ਜਾਂਦਾ ਹੈ, ਅਤੇ ਫਿਰ ਸੁਕਾਉਣ ਲਈ 100℃ 'ਤੇ ਇੱਕ ਓਵਨ ਵਿੱਚ ਰੱਖਿਆ ਜਾਂਦਾ ਹੈ। ਅੰਤ ਵਿੱਚ, ਗ੍ਰਾਫਾਈਟ ਸਬਸਟਰੇਟ ਨੂੰ SiC ਜਮ੍ਹਾਂ ਹੋਣ ਲਈ ਟਿਊਬਲਰ ਭੱਠੀ ਦੇ ਮੁੱਖ ਤਾਪਮਾਨ ਜ਼ੋਨ ਵਿੱਚ ਰੱਖਿਆ ਜਾਂਦਾ ਹੈ। ਰਸਾਇਣਕ ਭਾਫ਼ ਜਮ੍ਹਾਂ ਹੋਣ ਵਾਲੀ ਪ੍ਰਣਾਲੀ ਦਾ ਯੋਜਨਾਬੱਧ ਚਿੱਤਰ ਚਿੱਤਰ 1 ਵਿੱਚ ਦਿਖਾਇਆ ਗਿਆ ਹੈ।

ਦCVD SiC ਕੋਟਿੰਗਇਸਦੇ ਕਣਾਂ ਦੇ ਆਕਾਰ ਅਤੇ ਘਣਤਾ ਦਾ ਵਿਸ਼ਲੇਸ਼ਣ ਕਰਨ ਲਈ ਇਲੈਕਟ੍ਰੌਨ ਮਾਈਕ੍ਰੋਸਕੋਪੀ ਨੂੰ ਸਕੈਨ ਕਰਕੇ ਦੇਖਿਆ ਗਿਆ। ਇਸ ਤੋਂ ਇਲਾਵਾ, SiC ਕੋਟਿੰਗ ਦੀ ਜਮ੍ਹਾਂ ਦਰ ਦੀ ਗਣਨਾ ਹੇਠਾਂ ਦਿੱਤੇ ਫਾਰਮੂਲੇ ਅਨੁਸਾਰ ਕੀਤੀ ਗਈ ਸੀ: VSiC=(m2-m1)/(Sxt)x100% VSiC=ਜਮਾ ਦਰ; m2–ਪਰਤ ਦੇ ਨਮੂਨੇ ਦਾ ਪੁੰਜ (mg); m1–ਸਬਸਟਰੇਟ ਦਾ ਪੁੰਜ (mg); ਸਬਸਟਰੇਟ ਦਾ S-ਸਤਹ ਖੇਤਰ (mm2); t-ਜਮ੍ਹਾ ਸਮਾਂ (h)। CVD-SiC ਮੁਕਾਬਲਤਨ ਗੁੰਝਲਦਾਰ ਹੈ, ਅਤੇ ਇਸ ਪ੍ਰਕਿਰਿਆ ਦਾ ਸਾਰ ਇਸ ਤਰ੍ਹਾਂ ਦਿੱਤਾ ਜਾ ਸਕਦਾ ਹੈ: ਉੱਚ ਤਾਪਮਾਨ 'ਤੇ, MTS ਕਾਰਬਨ ਸਰੋਤ ਅਤੇ ਸਿਲੀਕਾਨ ਸਰੋਤ ਛੋਟੇ ਅਣੂ ਬਣਾਉਣ ਲਈ ਥਰਮਲ ਸੜਨ ਤੋਂ ਗੁਜ਼ਰੇਗਾ। ਕਾਰਬਨ ਸਰੋਤ ਛੋਟੇ ਅਣੂਆਂ ਵਿੱਚ ਮੁੱਖ ਤੌਰ 'ਤੇ CH3, C2H2 ਅਤੇ C2H4 ਸ਼ਾਮਲ ਹਨ, ਅਤੇ ਸਿਲੀਕਾਨ ਸਰੋਤ ਛੋਟੇ ਅਣੂਆਂ ਵਿੱਚ ਮੁੱਖ ਤੌਰ 'ਤੇ SiCI2, SiCI3, ਆਦਿ ਸ਼ਾਮਲ ਹਨ; ਇਹ ਕਾਰਬਨ ਸਰੋਤ ਅਤੇ ਸਿਲੀਕਾਨ ਸਰੋਤ ਛੋਟੇ ਅਣੂ ਫਿਰ ਕੈਰੀਅਰ ਗੈਸ ਅਤੇ ਪਤਲੇ ਗੈਸ ਦੁਆਰਾ ਗ੍ਰਾਫਾਈਟ ਸਬਸਟਰੇਟ ਦੀ ਸਤ੍ਹਾ 'ਤੇ ਲਿਜਾਏ ਜਾਣਗੇ, ਅਤੇ ਫਿਰ ਇਹ ਛੋਟੇ ਅਣੂ ਸੋਖਣ ਦੇ ਰੂਪ ਵਿੱਚ ਸਬਸਟਰੇਟ ਦੀ ਸਤ੍ਹਾ 'ਤੇ ਸੋਖ ਲਏ ਜਾਣਗੇ, ਅਤੇ ਫਿਰ ਛੋਟੇ ਅਣੂਆਂ ਵਿਚਕਾਰ ਰਸਾਇਣਕ ਪ੍ਰਤੀਕ੍ਰਿਆਵਾਂ ਹੋਣਗੀਆਂ ਤਾਂ ਜੋ ਛੋਟੀਆਂ ਬੂੰਦਾਂ ਬਣ ਸਕਣ ਜੋ ਹੌਲੀ-ਹੌਲੀ ਵਧਦੀਆਂ ਹਨ, ਅਤੇ ਬੂੰਦਾਂ ਵੀ ਫਿਊਜ਼ ਹੋ ਜਾਣਗੀਆਂ, ਅਤੇ ਪ੍ਰਤੀਕ੍ਰਿਆ ਵਿਚਕਾਰਲੇ ਉਪ-ਉਤਪਾਦਾਂ (HCl ਗੈਸ) ਦੇ ਗਠਨ ਦੇ ਨਾਲ ਹੋਵੇਗੀ; ਜਦੋਂ ਤਾਪਮਾਨ 1000 ℃ ਤੱਕ ਵਧਦਾ ਹੈ, ਤਾਂ SiC ਕੋਟਿੰਗ ਦੀ ਘਣਤਾ ਵਿੱਚ ਬਹੁਤ ਸੁਧਾਰ ਹੁੰਦਾ ਹੈ। ਇਹ ਦੇਖਿਆ ਜਾ ਸਕਦਾ ਹੈ ਕਿ ਜ਼ਿਆਦਾਤਰ ਕੋਟਿੰਗ SiC ਦਾਣਿਆਂ (ਲਗਭਗ 4μm ਆਕਾਰ) ਤੋਂ ਬਣੀ ਹੁੰਦੀ ਹੈ, ਪਰ ਕੁਝ ਰੇਸ਼ੇਦਾਰ SiC ਨੁਕਸ ਵੀ ਪਾਏ ਜਾਂਦੇ ਹਨ, ਜੋ ਦਰਸਾਉਂਦਾ ਹੈ ਕਿ ਇਸ ਤਾਪਮਾਨ 'ਤੇ SiC ਦਾ ਦਿਸ਼ਾ-ਨਿਰਦੇਸ਼ ਵਾਧਾ ਅਜੇ ਵੀ ਹੁੰਦਾ ਹੈ, ਅਤੇ ਕੋਟਿੰਗ ਅਜੇ ਵੀ ਕਾਫ਼ੀ ਸੰਘਣੀ ਨਹੀਂ ਹੈ। ਜਦੋਂ ਤਾਪਮਾਨ 1100 ℃ ਤੱਕ ਵਧਦਾ ਹੈ, ਤਾਂ ਇਹ ਦੇਖਿਆ ਜਾ ਸਕਦਾ ਹੈ ਕਿ SiC ਕੋਟਿੰਗ ਬਹੁਤ ਸੰਘਣੀ ਹੈ, ਅਤੇ ਰੇਸ਼ੇਦਾਰ SiC ਨੁਕਸ ਪੂਰੀ ਤਰ੍ਹਾਂ ਅਲੋਪ ਹੋ ਗਏ ਹਨ। ਕੋਟਿੰਗ ਲਗਭਗ 5~10μm ਦੇ ਵਿਆਸ ਵਾਲੇ ਬੂੰਦਾਂ-ਆਕਾਰ ਦੇ SiC ਕਣਾਂ ਤੋਂ ਬਣੀ ਹੁੰਦੀ ਹੈ, ਜੋ ਕਿ ਕੱਸ ਕੇ ਮਿਲਾਏ ਜਾਂਦੇ ਹਨ। ਕਣਾਂ ਦੀ ਸਤ੍ਹਾ ਬਹੁਤ ਖੁਰਦਰੀ ਹੁੰਦੀ ਹੈ। ਇਹ ਅਣਗਿਣਤ ਨੈਨੋ-ਸਕੇਲ SiC ਦਾਣਿਆਂ ਤੋਂ ਬਣੀ ਹੁੰਦੀ ਹੈ। ਦਰਅਸਲ, 1100 ℃ 'ਤੇ CVD-SiC ਵਿਕਾਸ ਪ੍ਰਕਿਰਿਆ ਪੁੰਜ ਟ੍ਰਾਂਸਫਰ ਨਿਯੰਤਰਿਤ ਹੋ ਗਈ ਹੈ। ਸਬਸਟਰੇਟ ਦੀ ਸਤ੍ਹਾ 'ਤੇ ਸੋਖੇ ਗਏ ਛੋਟੇ ਅਣੂਆਂ ਵਿੱਚ ਨਿਊਕਲੀਏਟ ਹੋਣ ਅਤੇ SiC ਦਾਣਿਆਂ ਵਿੱਚ ਵਧਣ ਲਈ ਕਾਫ਼ੀ ਊਰਜਾ ਅਤੇ ਸਮਾਂ ਹੁੰਦਾ ਹੈ। SiC ਦਾਣੇ ਇੱਕੋ ਜਿਹੇ ਵੱਡੇ ਬੂੰਦਾਂ ਬਣਾਉਂਦੇ ਹਨ। ਸਤ੍ਹਾ ਊਰਜਾ ਦੀ ਕਿਰਿਆ ਦੇ ਅਧੀਨ, ਜ਼ਿਆਦਾਤਰ ਬੂੰਦਾਂ ਗੋਲਾਕਾਰ ਦਿਖਾਈ ਦਿੰਦੀਆਂ ਹਨ, ਅਤੇ ਬੂੰਦਾਂ ਨੂੰ ਇੱਕ ਸੰਘਣੀ SiC ਪਰਤ ਬਣਾਉਣ ਲਈ ਕੱਸ ਕੇ ਜੋੜਿਆ ਜਾਂਦਾ ਹੈ। ਜਦੋਂ ਤਾਪਮਾਨ 1200℃ ਤੱਕ ਵਧਦਾ ਹੈ, ਤਾਂ SiC ਪਰਤ ਵੀ ਸੰਘਣੀ ਹੁੰਦੀ ਹੈ, ਪਰ SiC ਰੂਪ ਵਿਗਿਆਨ ਬਹੁ-ਛਾਲੇਦਾਰ ਹੋ ਜਾਂਦੀ ਹੈ ਅਤੇ ਪਰਤ ਦੀ ਸਤ੍ਹਾ ਖੁਰਦਰੀ ਦਿਖਾਈ ਦਿੰਦੀ ਹੈ। ਜਦੋਂ ਤਾਪਮਾਨ 1300℃ ਤੱਕ ਵਧਦਾ ਹੈ, ਤਾਂ ਗ੍ਰਾਫਾਈਟ ਸਬਸਟਰੇਟ ਦੀ ਸਤ੍ਹਾ 'ਤੇ ਲਗਭਗ 3μm ਦੇ ਵਿਆਸ ਵਾਲੇ ਨਿਯਮਤ ਗੋਲਾਕਾਰ ਕਣਾਂ ਦੀ ਇੱਕ ਵੱਡੀ ਗਿਣਤੀ ਪਾਈ ਜਾਂਦੀ ਹੈ। ਇਹ ਇਸ ਲਈ ਹੈ ਕਿਉਂਕਿ ਇਸ ਤਾਪਮਾਨ 'ਤੇ, SiC ਗੈਸ ਪੜਾਅ ਨਿਊਕਲੀਏਸ਼ਨ ਵਿੱਚ ਬਦਲ ਗਿਆ ਹੈ, ਅਤੇ MTS ਸੜਨ ਦੀ ਦਰ ਬਹੁਤ ਤੇਜ਼ ਹੈ। ਛੋਟੇ ਅਣੂਆਂ ਨੇ ਸਬਸਟਰੇਟ ਸਤ੍ਹਾ 'ਤੇ ਸੋਖਣ ਤੋਂ ਪਹਿਲਾਂ SiC ਅਨਾਜ ਬਣਾਉਣ ਲਈ ਪ੍ਰਤੀਕਿਰਿਆ ਕੀਤੀ ਹੈ ਅਤੇ ਨਿਊਕਲੀਏਟ ਕੀਤਾ ਹੈ। ਅਨਾਜ ਗੋਲਾਕਾਰ ਕਣ ਬਣਨ ਤੋਂ ਬਾਅਦ, ਉਹ ਹੇਠਾਂ ਡਿੱਗ ਜਾਣਗੇ, ਅੰਤ ਵਿੱਚ ਇੱਕ ਢਿੱਲੀ SiC ਕਣ ਪਰਤ ਦੇ ਨਤੀਜੇ ਵਜੋਂ ਘਟੀਆ ਘਣਤਾ ਹੁੰਦੀ ਹੈ। ਸਪੱਸ਼ਟ ਤੌਰ 'ਤੇ, 1300℃ ਨੂੰ ਸੰਘਣੀ SiC ਕੋਟਿੰਗ ਦੇ ਗਠਨ ਤਾਪਮਾਨ ਵਜੋਂ ਨਹੀਂ ਵਰਤਿਆ ਜਾ ਸਕਦਾ। ਵਿਆਪਕ ਤੁਲਨਾ ਦਰਸਾਉਂਦੀ ਹੈ ਕਿ ਜੇਕਰ ਸੰਘਣੀ SiC ਕੋਟਿੰਗ ਤਿਆਰ ਕਰਨੀ ਹੈ, ਤਾਂ ਅਨੁਕੂਲ CVD ਜਮ੍ਹਾ ਤਾਪਮਾਨ 1100℃ ਹੈ।

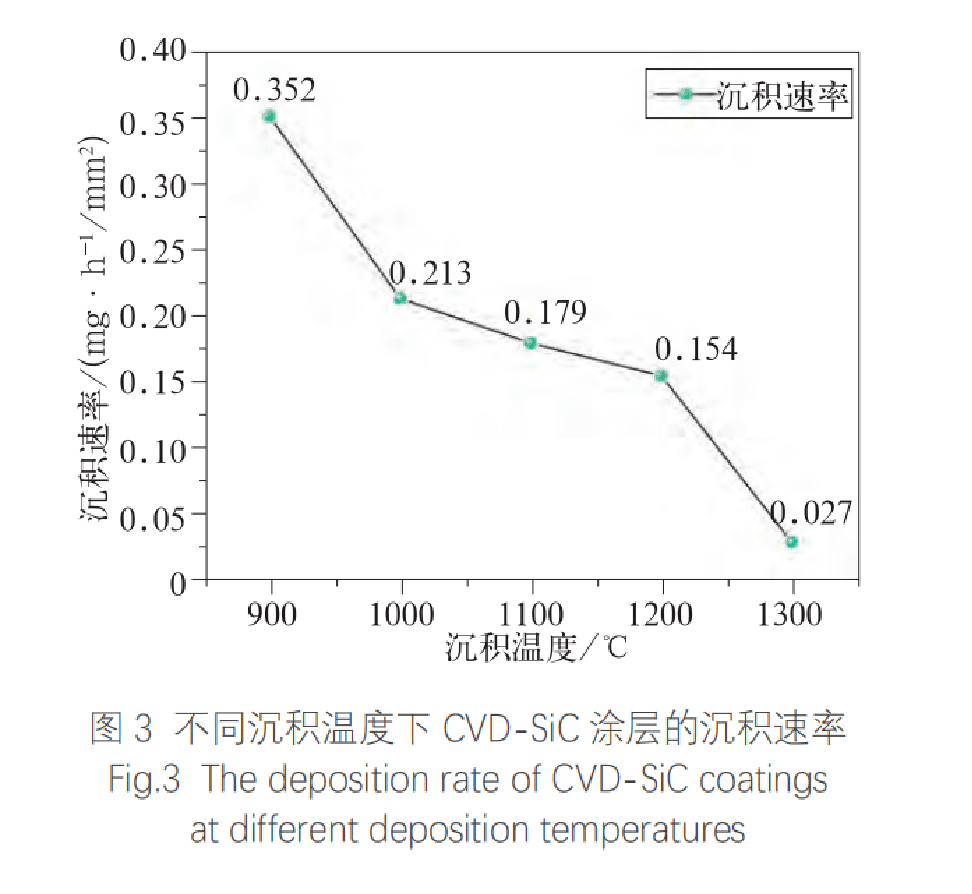

ਚਿੱਤਰ 3 ਵੱਖ-ਵੱਖ ਡਿਪੋਜ਼ਿਸ਼ਨ ਤਾਪਮਾਨਾਂ 'ਤੇ CVD SiC ਕੋਟਿੰਗਾਂ ਦੀ ਡਿਪੋਜ਼ਿਸ਼ਨ ਦਰ ਦਰਸਾਉਂਦਾ ਹੈ। ਜਿਵੇਂ-ਜਿਵੇਂ ਡਿਪੋਜ਼ਿਸ਼ਨ ਤਾਪਮਾਨ ਵਧਦਾ ਹੈ, SiC ਕੋਟਿੰਗ ਦੀ ਡਿਪੋਜ਼ਿਸ਼ਨ ਦਰ ਹੌਲੀ-ਹੌਲੀ ਘੱਟਦੀ ਜਾਂਦੀ ਹੈ। 900°C 'ਤੇ ਡਿਪੋਜ਼ਿਸ਼ਨ ਦਰ 0.352 mg·h-1/mm2 ਹੈ, ਅਤੇ ਰੇਸ਼ਿਆਂ ਦਾ ਦਿਸ਼ਾ-ਨਿਰਦੇਸ਼ ਵਿਕਾਸ ਸਭ ਤੋਂ ਤੇਜ਼ ਡਿਪੋਜ਼ਿਸ਼ਨ ਦਰ ਵੱਲ ਲੈ ਜਾਂਦਾ ਹੈ। ਸਭ ਤੋਂ ਵੱਧ ਘਣਤਾ ਵਾਲੀ ਕੋਟਿੰਗ ਦੀ ਡਿਪੋਜ਼ਿਸ਼ਨ ਦਰ 0.179 mg·h-1/mm2 ਹੈ। ਕੁਝ SiC ਕਣਾਂ ਦੇ ਡਿਪੋਜ਼ਿਸ਼ਨ ਦੇ ਕਾਰਨ, 1300°C 'ਤੇ ਡਿਪੋਜ਼ਿਸ਼ਨ ਦਰ ਸਭ ਤੋਂ ਘੱਟ ਹੈ, ਸਿਰਫ 0.027 mg·h-1/mm2। ਸਿੱਟਾ: ਸਭ ਤੋਂ ਵਧੀਆ CVD ਜਮ੍ਹਾ ਤਾਪਮਾਨ 1100℃ ਹੈ। ਘੱਟ ਤਾਪਮਾਨ SiC ਦੇ ਦਿਸ਼ਾਤਮਕ ਵਿਕਾਸ ਨੂੰ ਉਤਸ਼ਾਹਿਤ ਕਰਦਾ ਹੈ, ਜਦੋਂ ਕਿ ਉੱਚ ਤਾਪਮਾਨ SiC ਨੂੰ ਭਾਫ਼ ਜਮ੍ਹਾ ਕਰਨ ਦਾ ਕਾਰਨ ਬਣਦਾ ਹੈ ਅਤੇ ਨਤੀਜੇ ਵਜੋਂ ਸਪਾਰਸ ਕੋਟਿੰਗ ਹੁੰਦੀ ਹੈ। ਜਮ੍ਹਾ ਤਾਪਮਾਨ ਦੇ ਵਾਧੇ ਦੇ ਨਾਲ, ਜਮ੍ਹਾ ਦਰCVD SiC ਕੋਟਿੰਗਹੌਲੀ-ਹੌਲੀ ਘੱਟਦਾ ਹੈ।

ਪੋਸਟ ਸਮਾਂ: ਮਈ-26-2025