ত্রিকোণাকার ত্রুটি

ত্রিকোণাকার ত্রুটি হল SiC এপিট্যাক্সিয়াল স্তরের সবচেয়ে মারাত্মক রূপগত ত্রুটি। প্রচুর সংখ্যক সাহিত্য প্রতিবেদনে দেখা গেছে যে ত্রিকোণাকার ত্রুটির গঠন 3C স্ফটিকের সাথে সম্পর্কিত। তবে, বিভিন্ন বৃদ্ধি প্রক্রিয়ার কারণে, এপিট্যাক্সিয়াল স্তরের পৃষ্ঠে অনেক ত্রিকোণাকার ত্রুটির রূপগতি বেশ ভিন্ন। এটিকে মোটামুটিভাবে নিম্নলিখিত ধরণের মধ্যে ভাগ করা যেতে পারে:

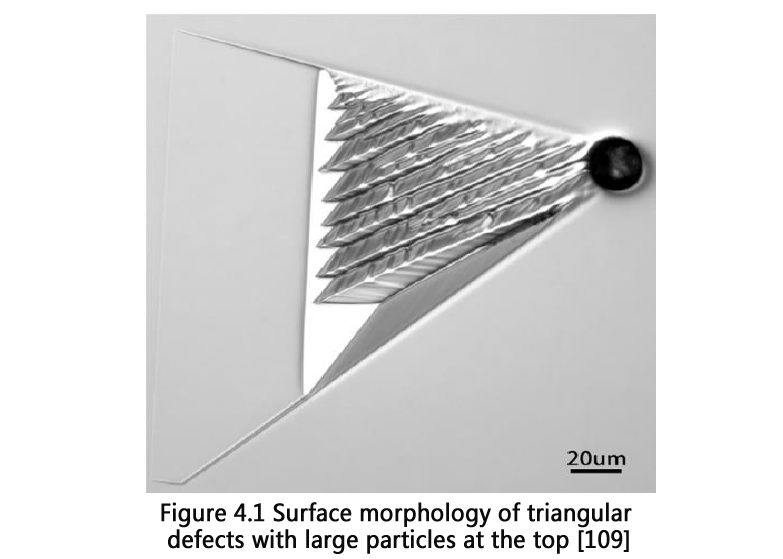

(১) উপরে বৃহৎ কণা সহ ত্রিভুজাকার ত্রুটি রয়েছে

এই ধরণের ত্রিভুজাকার ত্রুটির উপরে একটি বৃহৎ গোলাকার কণা থাকে, যা বৃদ্ধি প্রক্রিয়ার সময় বস্তুর পতনের কারণে হতে পারে। এই শীর্ষবিন্দু থেকে নীচের দিকে রুক্ষ পৃষ্ঠ সহ একটি ছোট ত্রিভুজাকার অঞ্চল লক্ষ্য করা যায়। এর কারণ হল এপিট্যাক্সিয়াল প্রক্রিয়া চলাকালীন, ত্রিভুজাকার অঞ্চলে দুটি ভিন্ন 3C-SiC স্তর ধারাবাহিকভাবে তৈরি হয়, যার মধ্যে প্রথম স্তরটি ইন্টারফেসে নিউক্লিয়েটেড হয় এবং 4H-SiC ধাপ প্রবাহের মাধ্যমে বৃদ্ধি পায়। এপিট্যাক্সিয়াল স্তরের পুরুত্ব বৃদ্ধির সাথে সাথে, 3C পলিটাইপের দ্বিতীয় স্তরটি নিউক্লিয়েটেড হয় এবং ছোট ত্রিভুজাকার গর্তে বৃদ্ধি পায়, তবে 4H বৃদ্ধি পদক্ষেপটি 3C পলিটাইপ অঞ্চলটিকে সম্পূর্ণরূপে আবৃত করে না, যার ফলে 3C-SiC এর V-আকৃতির খাঁজ অঞ্চলটি এখনও স্পষ্টভাবে দৃশ্যমান হয়।

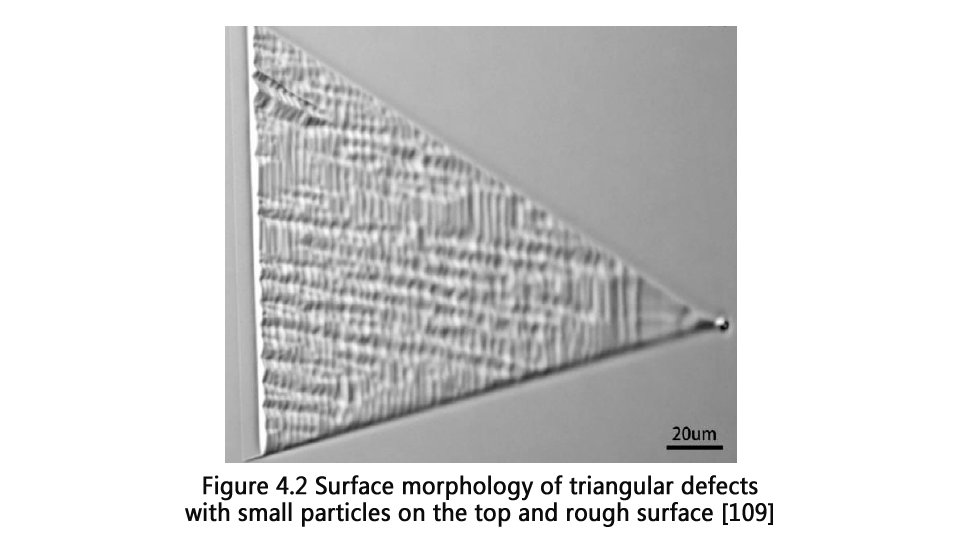

(২) উপরে ছোট ছোট কণা এবং রুক্ষ পৃষ্ঠ সহ ত্রিভুজাকার ত্রুটি রয়েছে

এই ধরণের ত্রিভুজাকার ত্রুটির শীর্ষবিন্দুতে অবস্থিত কণাগুলি চিত্র 4.2-এ দেখানো হয়েছে, যেমনটি অনেক ছোট। এবং ত্রিভুজাকার এলাকার বেশিরভাগ অংশ 4H-SiC এর ধাপ প্রবাহ দ্বারা আচ্ছাদিত, অর্থাৎ, সম্পূর্ণ 3C-SiC স্তরটি সম্পূর্ণরূপে 4H-SiC স্তরের নীচে এমবেড করা হয়েছে। ত্রিভুজাকার ত্রুটি পৃষ্ঠে কেবল 4H-SiC এর বৃদ্ধির ধাপগুলি দেখা যায়, তবে এই ধাপগুলি প্রচলিত 4H স্ফটিক বৃদ্ধির ধাপগুলির তুলনায় অনেক বড়।

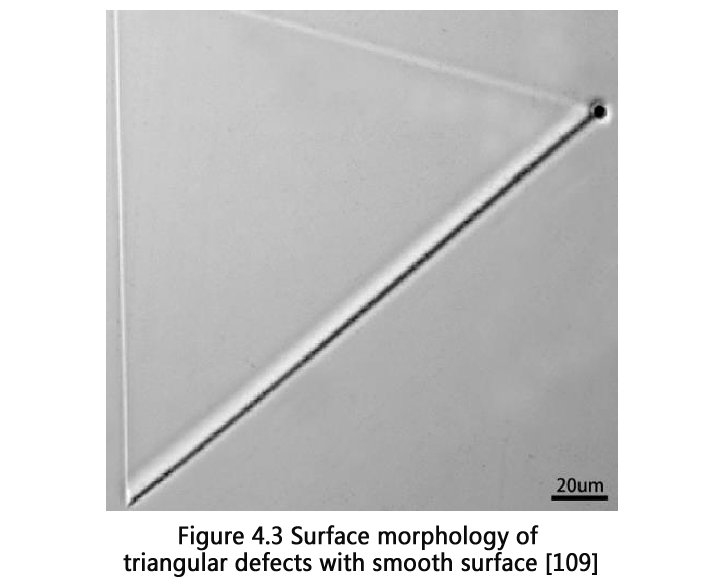

(3) মসৃণ পৃষ্ঠ সহ ত্রিকোণাকার ত্রুটি

এই ধরণের ত্রিভুজাকার ত্রুটির পৃষ্ঠের আকৃতি মসৃণ থাকে, যেমনটি চিত্র 4.3-এ দেখানো হয়েছে। এই ধরণের ত্রিভুজাকার ত্রুটির জন্য, 3C-SiC স্তরটি 4H-SiC এর ধাপ প্রবাহ দ্বারা আবৃত থাকে এবং পৃষ্ঠের 4H স্ফটিক আকৃতি আরও সূক্ষ্ম এবং মসৃণ হয়।

এপিট্যাক্সিয়াল পিট ত্রুটি

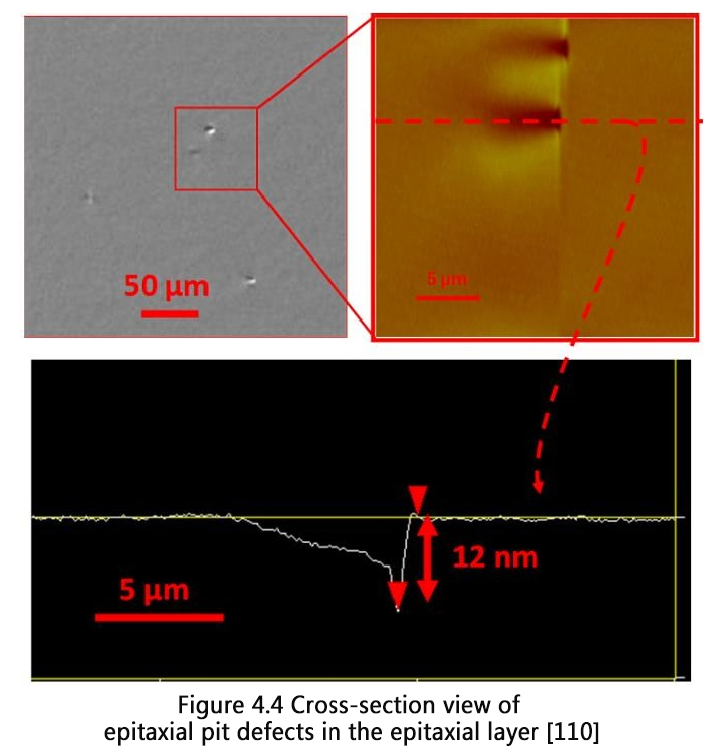

এপিট্যাক্সিয়াল পিট (পিটস) হল সবচেয়ে সাধারণ পৃষ্ঠের আকারবিদ্যা ত্রুটিগুলির মধ্যে একটি, এবং তাদের সাধারণ পৃষ্ঠের আকারবিদ্যা এবং কাঠামোগত রূপরেখা চিত্র 4.4 এ দেখানো হয়েছে। ডিভাইসের পিছনে KOH এচিংয়ের পরে পর্যবেক্ষণ করা থ্রেডিং ডিসলোকেশন (TD) জারা পিটের অবস্থান ডিভাইস প্রস্তুতির আগে এপিট্যাক্সিয়াল পিটের অবস্থানের সাথে স্পষ্টভাবে মিলিত হয়, যা নির্দেশ করে যে এপিট্যাক্সিয়াল পিট ত্রুটিগুলির গঠন থ্রেডিং ডিসলোকেশনের সাথে সম্পর্কিত।

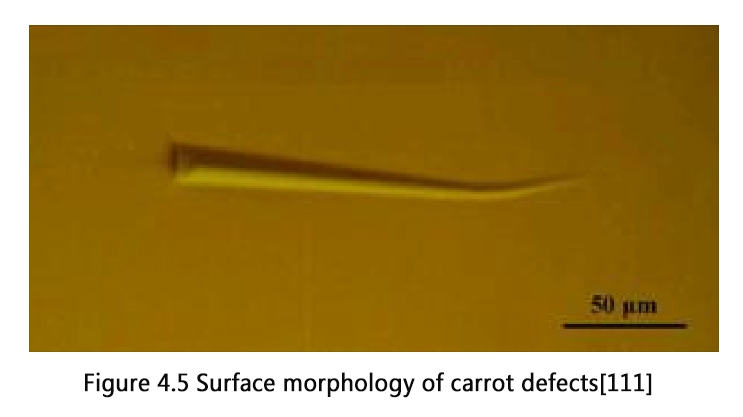

গাজরের ত্রুটি

4H-SiC এপিট্যাক্সিয়াল স্তরগুলিতে গাজরের ত্রুটি একটি সাধারণ পৃষ্ঠ ত্রুটি, এবং তাদের সাধারণ রূপবিদ্যা চিত্র 4.5 এ দেখানো হয়েছে। ধাপের মতো স্থানচ্যুতি দ্বারা সংযুক্ত বেসাল সমতলে অবস্থিত ফ্রাঙ্কোনিয়ান এবং প্রিজম্যাটিক স্ট্যাকিং ফল্টের ছেদ দ্বারা গাজরের ত্রুটি তৈরি হয় বলে জানা গেছে। এটিও রিপোর্ট করা হয়েছে যে গাজরের ত্রুটির গঠন সাবস্ট্রেটে TSD এর সাথে সম্পর্কিত। সুচিদা এইচ. এট আল. দেখেছেন যে এপিট্যাক্সিয়াল স্তরে গাজরের ত্রুটির ঘনত্ব সাবস্ট্রেটে TSD এর ঘনত্বের সমানুপাতিক। এবং এপিট্যাক্সিয়াল বৃদ্ধির আগে এবং পরে পৃষ্ঠের রূপবিদ্যা চিত্রগুলির তুলনা করে, সমস্ত পর্যবেক্ষণ করা গাজরের ত্রুটিগুলি সাবস্ট্রেটে TSD এর সাথে সঙ্গতিপূর্ণ বলে পাওয়া যেতে পারে। উ এইচ. এট আল. রমন স্ক্যাটারিং পরীক্ষার চরিত্রায়ন ব্যবহার করে আবিষ্কার করেছেন যে গাজরের ত্রুটিগুলিতে 3C স্ফটিক ফর্ম ছিল না, তবে কেবল 4H-SiC পলিটাইপ ছিল।

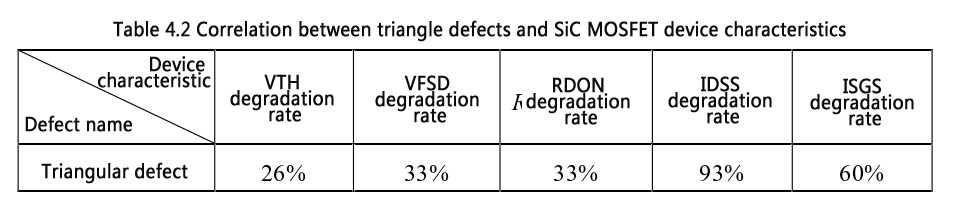

MOSFET ডিভাইসের বৈশিষ্ট্যের উপর ত্রিভুজাকার ত্রুটির প্রভাব

চিত্র ৪.৭ হল ত্রিভুজাকার ত্রুটিযুক্ত একটি ডিভাইসের পাঁচটি বৈশিষ্ট্যের পরিসংখ্যানগত বন্টনের একটি হিস্টোগ্রাম। নীল বিন্দুযুক্ত রেখাটি ডিভাইসের বৈশিষ্ট্যগত অবক্ষয়ের জন্য বিভাজক রেখা এবং লাল বিন্দুযুক্ত রেখাটি ডিভাইসের ব্যর্থতার জন্য বিভাজক রেখা। ডিভাইসের ব্যর্থতার জন্য, ত্রিভুজাকার ত্রুটিগুলির একটি বড় প্রভাব রয়েছে এবং ব্যর্থতার হার ৯৩% এর বেশি। এটি মূলত ডিভাইসের বিপরীত ফুটো বৈশিষ্ট্যের উপর ত্রিভুজাকার ত্রুটির প্রভাবের জন্য দায়ী। ত্রিভুজাকার ত্রুটিযুক্ত ৯৩% পর্যন্ত ডিভাইসের বিপরীত ফুটো উল্লেখযোগ্যভাবে বৃদ্ধি পেয়েছে। এছাড়াও, ত্রিভুজাকার ত্রুটিগুলি গেট ফুটো বৈশিষ্ট্যের উপরও গুরুতর প্রভাব ফেলে, যার অবক্ষয় হার ৬০%। সারণি ৪.২-তে দেখানো হয়েছে, থ্রেশহোল্ড ভোল্টেজ অবক্ষয় এবং বডি ডায়োড বৈশিষ্ট্যগত অবক্ষয়ের জন্য, ত্রিভুজাকার ত্রুটির প্রভাব ছোট এবং অবক্ষয়ের অনুপাত যথাক্রমে ২৬% এবং ৩৩%। অন-রেজিস্ট্যান্স বৃদ্ধির ক্ষেত্রে, ত্রিভুজাকার ত্রুটির প্রভাব দুর্বল এবং অবক্ষয় অনুপাত প্রায় ৩৩%।

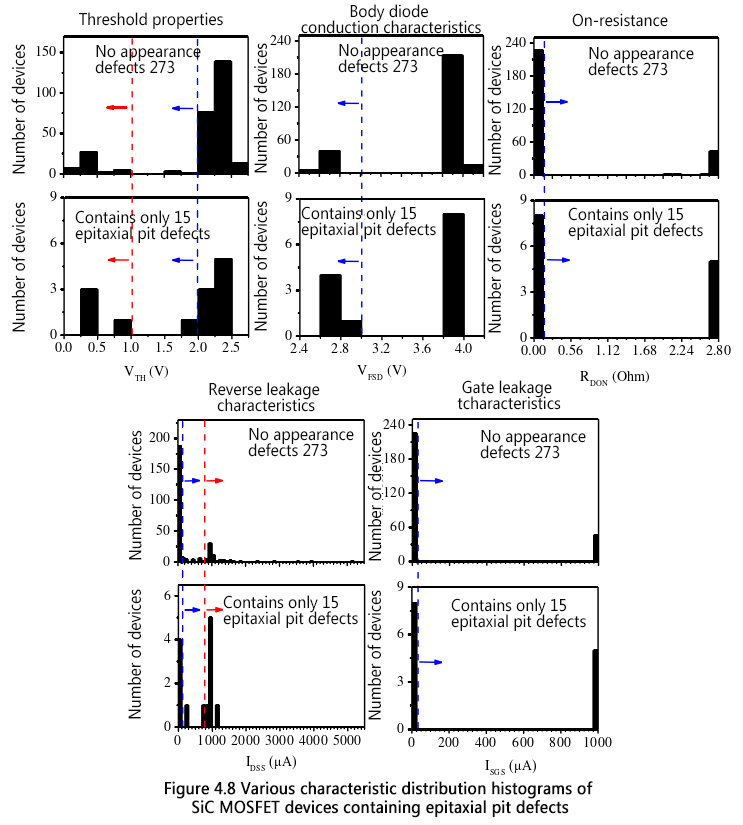

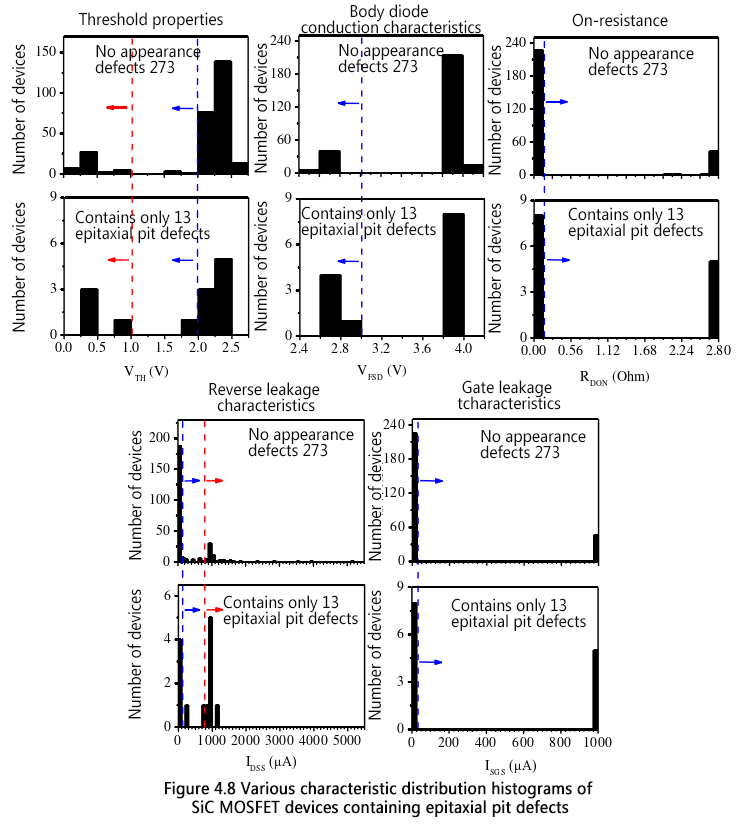

MOSFET ডিভাইসের বৈশিষ্ট্যের উপর এপিট্যাক্সিয়াল পিট ত্রুটির প্রভাব

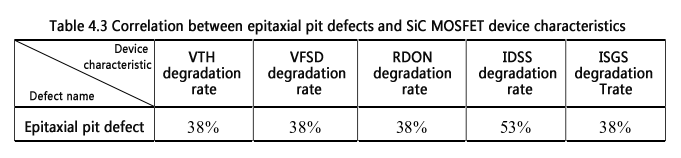

চিত্র ৪.৮ হল এপিট্যাক্সিয়াল পিট ত্রুটিযুক্ত একটি ডিভাইসের পাঁচটি বৈশিষ্ট্যের পরিসংখ্যানগত বন্টনের একটি হিস্টোগ্রাম। নীল বিন্দুযুক্ত রেখাটি ডিভাইসের বৈশিষ্ট্যগত অবক্ষয়ের জন্য বিভাজক রেখা এবং লাল বিন্দুযুক্ত রেখাটি ডিভাইসের ব্যর্থতার জন্য বিভাজক রেখা। এ থেকে দেখা যায় যে SiC MOSFET নমুনায় এপিট্যাক্সিয়াল পিট ত্রুটিযুক্ত ডিভাইসের সংখ্যা ত্রিভুজাকার ত্রুটিযুক্ত ডিভাইসের সংখ্যার সমান। ডিভাইসের বৈশিষ্ট্যের উপর এপিট্যাক্সিয়াল পিট ত্রুটির প্রভাব ত্রিভুজাকার ত্রুটির থেকে আলাদা। ডিভাইসের ব্যর্থতার ক্ষেত্রে, এপিট্যাক্সিয়াল পিট ত্রুটিযুক্ত ডিভাইসের ব্যর্থতার হার মাত্র ৪৭%। ত্রিভুজাকার ত্রুটির তুলনায়, ডিভাইসের বিপরীত লিকেজ বৈশিষ্ট্য এবং গেট লিকেজ বৈশিষ্ট্যের উপর এপিট্যাক্সিয়াল পিট ত্রুটির প্রভাব উল্লেখযোগ্যভাবে দুর্বল হয়ে পড়েছে, যার অবক্ষয় অনুপাত যথাক্রমে ৫৩% এবং ৩৮%, যেমনটি সারণি ৪.৩-এ দেখানো হয়েছে। অন্যদিকে, থ্রেশহোল্ড ভোল্টেজ বৈশিষ্ট্য, বডি ডায়োড পরিবাহী বৈশিষ্ট্য এবং অন-রেজিস্ট্যান্সের উপর এপিট্যাক্সিয়াল পিট ত্রুটির প্রভাব ত্রিভুজাকার ত্রুটির তুলনায় বেশি, অবক্ষয় অনুপাত ৩৮% এ পৌঁছেছে।

সাধারণভাবে, দুটি রূপগত ত্রুটি, যথা ত্রিভুজাকার এবং এপিট্যাক্সিয়াল পিট, SiC MOSFET ডিভাইসের ব্যর্থতা এবং বৈশিষ্ট্যগত অবক্ষয়ের উপর উল্লেখযোগ্য প্রভাব ফেলে। ত্রিভুজাকার ত্রুটির অস্তিত্ব সবচেয়ে মারাত্মক, যার ব্যর্থতার হার 93% পর্যন্ত, যা মূলত ডিভাইসের বিপরীত ফুটোতে উল্লেখযোগ্য বৃদ্ধি হিসাবে প্রকাশিত হয়। এপিট্যাক্সিয়াল পিট ত্রুটিযুক্ত ডিভাইসগুলির ব্যর্থতার হার 47% কম ছিল। তবে, এপিট্যাক্সিয়াল পিট ত্রুটিগুলি ত্রিভুজাকার ত্রুটির তুলনায় ডিভাইসের থ্রেশহোল্ড ভোল্টেজ, বডি ডায়োড পরিবাহী বৈশিষ্ট্য এবং অন-রেজিস্ট্যান্সের উপর বেশি প্রভাব ফেলে।

পোস্টের সময়: এপ্রিল-১৬-২০২৪