Quy trình BCD là gì?

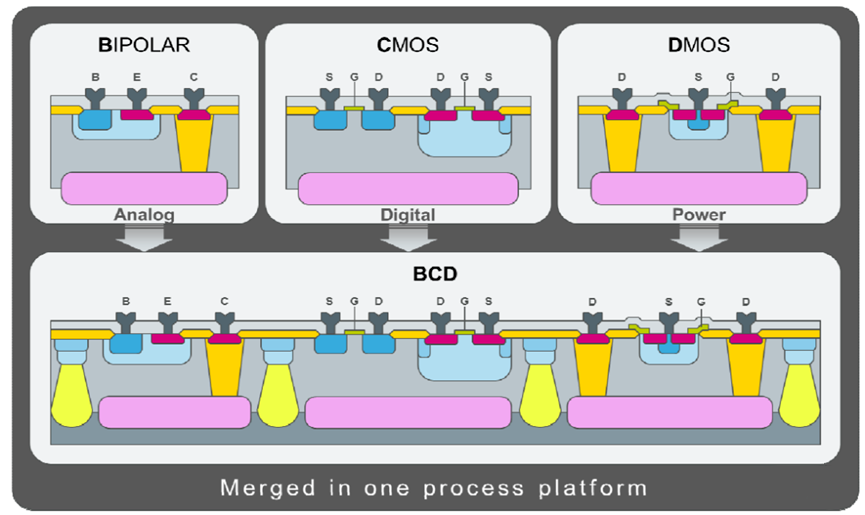

Quá trình BCD là công nghệ quá trình tích hợp chip đơn được ST giới thiệu lần đầu tiên vào năm 1986. Công nghệ này có thể tạo ra các thiết bị lưỡng cực, CMOS và DMOS trên cùng một chip. Sự xuất hiện của nó làm giảm đáng kể diện tích của chip.

Có thể nói rằng quy trình BCD tận dụng tối đa các ưu điểm của khả năng dẫn động lưỡng cực, tích hợp cao CMOS và tiêu thụ điện năng thấp, và khả năng lưu lượng dòng điện cao và điện áp cao DMOS. Trong số đó, DMOS là chìa khóa để cải thiện công suất và tích hợp. Với sự phát triển hơn nữa của công nghệ mạch tích hợp, quy trình BCD đã trở thành công nghệ sản xuất chủ đạo của PMIC.

Sơ đồ mặt cắt ngang quá trình BCD, mạng nguồn, cảm ơn bạn

Ưu điểm của quy trình BCD

Quá trình BCD tạo ra các thiết bị lưỡng cực, thiết bị CMOS và thiết bị nguồn DMOS trên cùng một chip cùng một lúc, tích hợp độ dẫn điện cao và khả năng dẫn tải mạnh của các thiết bị lưỡng cực và khả năng tích hợp cao và mức tiêu thụ điện năng thấp của CMOS, để chúng có thể bổ sung cho nhau và phát huy hết các lợi thế tương ứng của chúng; đồng thời, DMOS có thể hoạt động ở chế độ chuyển mạch với mức tiêu thụ điện năng cực thấp. Tóm lại, mức tiêu thụ điện năng thấp, hiệu suất năng lượng cao và mức tích hợp cao là một trong những ưu điểm chính của BCD. Quá trình BCD có thể giảm đáng kể mức tiêu thụ điện năng, cải thiện hiệu suất hệ thống và có độ tin cậy tốt hơn. Các chức năng của sản phẩm điện tử ngày càng tăng lên và các yêu cầu về thay đổi điện áp, bảo vệ tụ điện và kéo dài tuổi thọ pin ngày càng trở nên quan trọng. Các đặc tính tốc độ cao và tiết kiệm năng lượng của BCD đáp ứng các yêu cầu quy trình đối với chip quản lý nguồn/tương tự hiệu suất cao.

Công nghệ chính của quy trình BCD

Các thiết bị điển hình của quy trình BCD bao gồm CMOS điện áp thấp, ống MOS điện áp cao, LDMOS với nhiều điện áp đánh thủng khác nhau, NPN/PNP thẳng đứng và điốt Schottky, v.v. Một số quy trình cũng tích hợp các thiết bị như JFET và EEPROM, tạo ra nhiều loại thiết bị trong quy trình BCD. Do đó, ngoài việc xem xét tính tương thích của các thiết bị điện áp cao và thiết bị điện áp thấp, quy trình nhấp đúp và quy trình CMOS, v.v. trong thiết kế, công nghệ cách ly thích hợp cũng phải được xem xét.

Trong công nghệ cách ly BCD, nhiều công nghệ như cách ly mối nối, tự cách ly và cách ly điện môi đã lần lượt xuất hiện. Công nghệ cách ly mối nối là chế tạo thiết bị trên lớp epitaxial loại N của chất nền loại P và sử dụng đặc tính phân cực ngược của mối nối PN để đạt được sự cách ly, vì mối nối PN có điện trở rất cao dưới phân cực ngược.

Công nghệ tự cô lập về cơ bản là cách ly tiếp giáp PN, dựa trên đặc điểm tiếp giáp PN tự nhiên giữa vùng nguồn và vùng thoát của thiết bị và chất nền để đạt được sự cô lập. Khi ống MOS được bật, vùng nguồn, vùng thoát và kênh được bao quanh bởi vùng cạn kiệt, tạo thành sự cô lập khỏi chất nền. Khi nó bị tắt, mối nối PN giữa vùng thoát và chất nền bị phân cực ngược và điện áp cao của vùng nguồn được cô lập bởi vùng cạn kiệt.

Cách điện sử dụng vật liệu cách điện như oxit silic để đạt được sự cách điện. Dựa trên cách điện và cách điện mối nối, cách điện bán điện đã được phát triển bằng cách kết hợp các ưu điểm của cả hai. Bằng cách áp dụng có chọn lọc công nghệ cách điện trên, có thể đạt được khả năng tương thích điện áp cao và điện áp thấp.

Hướng phát triển của quy trình BCD

Sự phát triển của công nghệ quy trình BCD không giống như quy trình CMOS tiêu chuẩn, vốn luôn tuân theo định luật Moore để phát triển theo hướng chiều rộng đường nhỏ hơn và tốc độ nhanh hơn. Quy trình BCD được phân biệt sơ bộ và phát triển theo ba hướng: điện áp cao, công suất cao và mật độ cao.

1. Hướng BCD điện áp cao

BCD điện áp cao có thể sản xuất mạch điều khiển điện áp thấp có độ tin cậy cao và mạch cấp DMOS điện áp cực cao trên cùng một chip cùng một lúc và có thể thực hiện sản xuất các thiết bị điện áp cao 500-700V. Tuy nhiên, nhìn chung, BCD vẫn phù hợp với các sản phẩm có yêu cầu tương đối cao đối với các thiết bị công suất, đặc biệt là các thiết bị BJT hoặc DMOS dòng điện cao và có thể được sử dụng để điều khiển công suất trong chiếu sáng điện tử và các ứng dụng công nghiệp.

Công nghệ hiện tại để sản xuất BCD điện áp cao là công nghệ RESURF do Appel và cộng sự đề xuất vào năm 1979. Thiết bị được chế tạo bằng cách sử dụng lớp epitaxial pha tạp nhẹ để làm cho sự phân bố trường điện bề mặt phẳng hơn, do đó cải thiện các đặc tính đánh thủng bề mặt, do đó sự đánh thủng xảy ra trong thân thay vì bề mặt, do đó làm tăng điện áp đánh thủng của thiết bị. Pha tạp nhẹ là một phương pháp khác để tăng điện áp đánh thủng của BCD. Nó chủ yếu sử dụng cống khuếch tán kép DDD (dòng xả pha tạp kép) và cống pha tạp nhẹ LDD (dòng xả pha tạp nhẹ). Trong vùng cống DMOS, một vùng trôi loại N được thêm vào để thay đổi tiếp xúc ban đầu giữa cống N+ và chất nền loại P thành tiếp xúc giữa cống N- và chất nền loại P, do đó làm tăng điện áp đánh thủng.

2. Hướng BCD công suất cao

Phạm vi điện áp của BCD công suất cao là 40-90V, chủ yếu được sử dụng trong các thiết bị điện tử ô tô đòi hỏi khả năng dẫn động dòng điện cao, điện áp trung bình và mạch điều khiển đơn giản. Đặc điểm nhu cầu của nó là khả năng dẫn động dòng điện cao, điện áp trung bình và mạch điều khiển thường tương đối đơn giản.

3. Hướng BCD mật độ cao

BCD mật độ cao, phạm vi điện áp là 5-50V, và một số thiết bị điện tử ô tô sẽ đạt tới 70V. Ngày càng có nhiều chức năng phức tạp và đa dạng có thể được tích hợp trên cùng một chip. BCD mật độ cao áp dụng một số ý tưởng thiết kế mô-đun để đạt được sự đa dạng hóa sản phẩm, chủ yếu được sử dụng trong các ứng dụng điện tử ô tô.

Ứng dụng chính của quy trình BCD

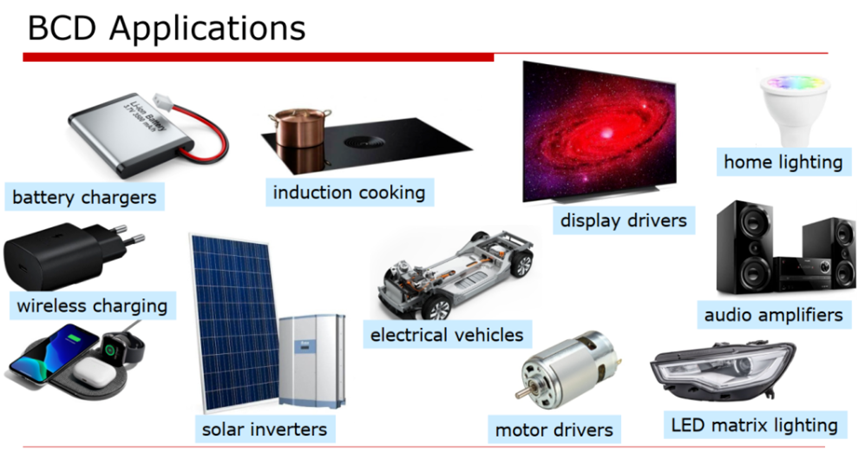

Quá trình BCD được sử dụng rộng rãi trong quản lý năng lượng (điều khiển nguồn và pin), ổ đĩa hiển thị, điện tử ô tô, điều khiển công nghiệp, v.v. Chip quản lý năng lượng (PMIC) là một trong những loại chip tương tự quan trọng. Sự kết hợp giữa quá trình BCD và công nghệ SOI cũng là một tính năng chính trong quá trình phát triển của quá trình BCD.

VET-China có thể cung cấp các bộ phận bằng than chì, nỉ mềm, các bộ phận bằng silicon carbide, các bộ phận bằng silicon carbide cvD và các bộ phận phủ sic/Tac trong vòng 30 ngày.

Nếu bạn quan tâm đến các sản phẩm bán dẫn nêu trên, vui lòng đừng ngần ngại liên hệ với chúng tôi ngay.

Điện thoại: +86-1891 1596 392

WhatsApp: 86-18069021720

E-mail:yeah@china-vet.com

Thời gian đăng: 18-09-2024