Wat ass de BCD-Prozess?

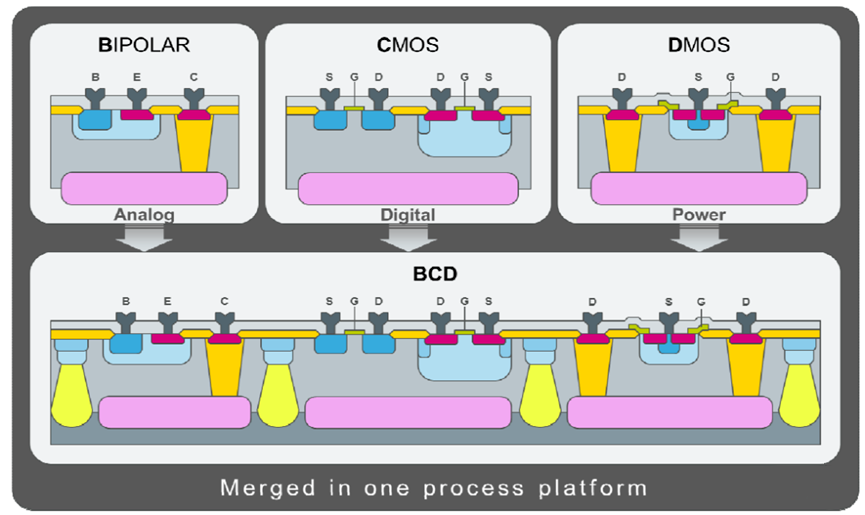

De BCD-Prozess ass eng integréiert Prozesstechnologie mat engem eenzege Chip, déi fir d'éischt vun ST am Joer 1986 agefouert gouf. Dës Technologie kann bipolar, CMOS- an DMOS-Geräter um selwechte Chip erstellen. Säin Optrëtt reduzéiert d'Fläch vum Chip däitlech.

Et kann ee soen, datt de BCD-Prozess d'Virdeeler vun der bipolarer Undriffskapazitéit, der héijer CMOS-Integratioun an dem niddrege Stroumverbrauch, souwéi der DMOS-Héichspannung an dem héije Stroumflusskapazitéit voll ausnotzt. Dorënner ass DMOS de Schlëssel fir d'Verbesserung vun der Leeschtung an der Integratioun. Mat der weiderer Entwécklung vun der integréierter Schaltungstechnologie ass de BCD-Prozess zur Mainstream-Fabrikatiounstechnologie vu PMIC ginn.

BCD Prozess Querschnittsdiagramm, Quellnetz, merci

Virdeeler vum BCD-Prozess

De BCD-Prozess mécht bipolare Geräter, CMOS-Geräter an DMOS-Stroumversuergungsgeräter gläichzäiteg um selwechte Chip, andeems déi héich Transkonduktanz an déi staark Lastdreiwkapazitéit vu bipolare Geräter an déi héich Integratioun an de niddrege Stroumverbrauch vu CMOS integréiert ginn, sou datt se sech géigesäiteg ergänze kënnen an hir jeeweileg Virdeeler voll ausnotze kënnen; gläichzäiteg kann DMOS am Schaltmodus mat extrem niddregem Stroumverbrauch funktionéieren. Kuerz gesot, niddrege Stroumverbrauch, héich Energieeffizienz an héich Integratioun sinn ee vun den Haaptvirdeeler vu BCD. De BCD-Prozess kann de Stroumverbrauch däitlech reduzéieren, d'Systemleistung verbesseren an eng besser Zouverlässegkeet hunn. D'Funktioune vun elektronesche Produkter huelen all Dag zou, an d'Ufuerderunge fir Spannungsännerungen, Kondensatorschutz a Batterielaufzäitverlängerung ginn ëmmer méi wichteg. Déi héich Geschwindegkeet an energiespuerend Charakteristike vu BCD erfëllen d'Prozesufuerderunge fir héich performant Analog-/Stroummanagement-Chips.

Schlësseltechnologien vum BCD-Prozess

Typesch Apparater vum BCD-Prozess sinn Nidderspannungs-CMOS, Héichspannungs-MOS-Röhren, LDMOS mat verschiddenen Duerchbrochspannungen, vertikal NPN/PNP- a Schottky-Dioden, etc. E puer Prozesser integréieren och Apparater wéi JFET an EEPROM, wat zu enger grousser Villfalt vun Apparater am BCD-Prozess féiert. Dofir muss, nieft der Berécksiichtegung vun der Kompatibilitéit vun Héichspannungs- an Nidderspannungs-Apparater, Double-Click-Prozesser a CMOS-Prozesser, etc. am Design, och déi entspriechend Isolatiounstechnologie berécksiichtegt ginn.

An der BCD-Isolatiounstechnologie sinn eng nom aneren eng Rei Technologien opgetrueden, wéi zum Beispill d'Isolatioun vun de Verbindungen, d'Selbstisolatioun an d'dielektresch Isolatioun. D'Technologie vun der Verbindungsisolatioun besteet doran, den Apparat op der epitaktischer N-Typ-Schicht vum P-Typ-Substrat ze placéieren an d'Charakteristike vun der PN-Verbindung mat Réckwärtsvirspannung ze benotzen, fir d'Isolatioun z'erreechen, well d'PN-Verbindung e ganz héije Widderstand ënner Réckwärtsvirspannung huet.

Selbstisolatiounstechnologie ass am Fong eng PN-Verbindungsisolatioun, déi sech op déi natierlech PN-Verbindungscharakteristiken tëscht der Quell- an der Drainregioun vum Apparat an dem Substrat baséiert, fir eng Isolatioun z'erreechen. Wann d'MOS-Röhre ageschalt ass, sinn d'Sourceregioun, d'Drainregioun an de Kanal vun der Depletiounsregioun ëmginn, wouduerch eng Isolatioun vum Substrat entsteet. Wann se ausgeschalt ass, gëtt d'PN-Verbindung tëscht der Drainregioun an dem Substrat ëmgedréint verspannt, an d'Héichspannung vun der Quellregioun gëtt vun der Depletiounsregioun isoléiert.

Dielektresch Isolatioun benotzt isoléierend Medien wéi Siliziumoxid fir d'Isolatioun z'erreechen. Baséierend op dielektrescher Isolatioun an Junction-Isolatioun gouf quasi-dielektresch Isolatioun entwéckelt andeems d'Virdeeler vun deenen zwou kombinéiert goufen. Duerch d'selektiv Uwendung vun der uewe genannter Isolatiounstechnologie kann Héichspannungs- a Nidderspannungskompatibilitéit erreecht ginn.

Entwécklungsrichtung vum BCD-Prozess

D'Entwécklung vun der BCD-Prozesstechnologie ass net wéi de Standard-CMOS-Prozess, deen ëmmer dem Moore-Gesetz gefollegt ass, fir sech a Richtung vun enger méi klenger Linnbreet a méi héijer Geschwindegkeet z'entwéckelen. De BCD-Prozess ass grob differenzéiert an an dräi Richtungen entwéckelt: Héichspannung, héich Leeschtung an héich Dicht.

1. Héichspannungs-BCD-Richtung

Héichspannungs-BCD kann gläichzäiteg héichzouverlässeg Nidderspannungs-Steierschaltkreesser a Ultra-Héichspannungs-DMOS-Level-Schaltkreesser um selwechte Chip hierstellen, a kann d'Produktioun vun 500-700V Héichspannungsgeräter realiséieren. Am Allgemengen ass BCD awer ëmmer nach gëeegent fir Produkter mat relativ héijen Ufuerderungen un Energieversuergungsgeräter, besonnesch BJT- oder Héichstroum-DMOS-Geräter, a kann fir d'Energiesteierung an der elektronescher Beliichtung an industriellen Uwendungen agesat ginn.

Déi aktuell Technologie fir d'Produktioun vun Héichspannungs-BCD ass d'RESURF-Technologie, déi vum Appel et al. am Joer 1979 proposéiert gouf. Den Apparat gëtt mat enger liicht dotierter epitaktischer Schicht hiergestallt, fir d'Verdeelung vum elektresche Feld op der Uewerfläch méi flaach ze maachen, wouduerch d'Charakteristike vum Duerchbroch vun der Uewerfläch verbessert ginn, sou datt den Duerchbroch am Kierper amplaz vun der Uewerfläch geschitt, wouduerch d'Duerchbrochspannung vum Apparat eropgeet. Liichtdotierung ass eng aner Method fir d'Duerchbrochspannung vun der BCD ze erhéijen. Si benotzt haaptsächlech duebel diffus Drain DDD (double Doping Drain) a liicht dotiert Drain LDD (lightly Doping Drain). An der DMOS-Drainregioun gëtt eng N-Typ Driftregioun bäigefüügt, fir den urspréngleche Kontakt tëscht dem N+ Drain an dem P-Typ Substrat an de Kontakt tëscht dem N- Drain an dem P-Typ Substrat z'änneren, wouduerch d'Duerchbrochspannung eropgeet.

2. Héichleistungs-BCD-Richtung

De Spannungsberäich vun engem BCD mat héijer Leeschtung läit tëscht 40 a 90 V, an et gëtt haaptsächlech an der Automobilelektronik benotzt, déi eng héich Stroumleistung, Mëttelspannung a einfach Steierschaltkreesser erfuerdert. Seng Nofrocharakteristike sinn eng héich Stroumleistung, Mëttelspannung, an de Steierschaltkrees ass dacks relativ einfach.

3. BCD-Richtung mat héijer Dicht

BCD mat héijer Dicht, de Spannungsberäich ass 5-50V, an e puer Automobilelektronikprodukter erreechen 70V. Ëmmer méi komplex a divers Funktiounen kënnen um selwechte Chip integréiert ginn. BCD mat héijer Dicht benotzt e puer modulare Designiddien fir eng Produktdiversifikatioun z'erreechen, haaptsächlech an Automobilelektronikapplikatiounen.

Haaptapplikatioune vum BCD-Prozess

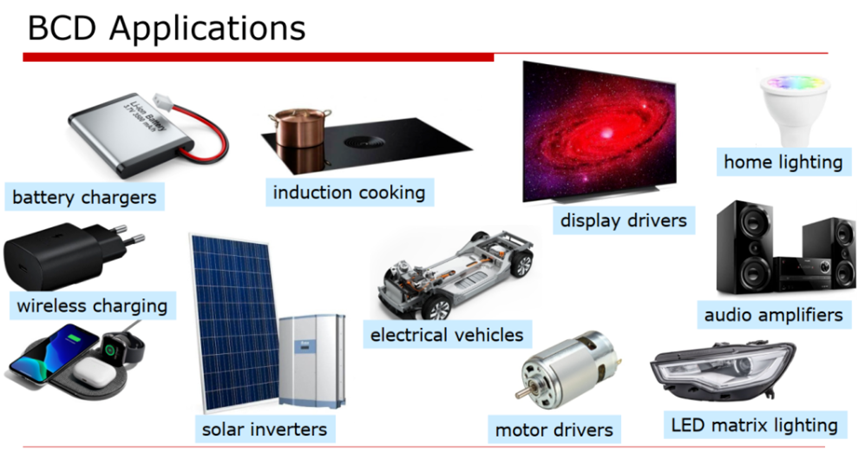

De BCD-Prozess gëtt wäit verbreet am Energiemanagement (Energie- a Batteriekontroll), Display-Undriff, Autoelektronik, Industriekontroll, etc. agesat. De Power Management Chip (PMIC) ass eng vun de wichtegsten Aarte vun analoge Chips. D'Kombinatioun vum BCD-Prozess an der SOI-Technologie ass och e wichtegt Merkmal vun der Entwécklung vum BCD-Prozess.

VET-China kann Graphitdeeler, mëllen, steife Filz, Siliziumcarbiddeeler, CVD-Siliziumcarbiddeeler a SIC/TAC-beschichtete Deeler bannent 30 Deeg liwweren.

Wann Dir un den uewe genannten Hallefleederprodukter interesséiert sidd, zéckt net eis als éischt ze kontaktéieren.

Tel.: +86-1891 1596 392

WhatsApp: 86-18069021720

E-Mail:yeah@china-vet.com

Zäitpunkt vun der Verëffentlechung: 18. September 2024