กระบวนการ BCD คืออะไร?

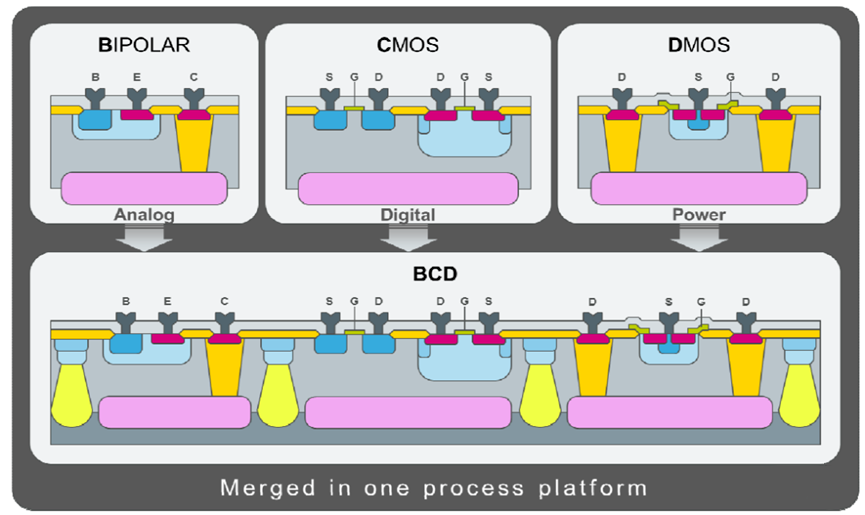

กระบวนการ BCD เป็นเทคโนโลยีกระบวนการแบบรวมชิปตัวเดียวที่เปิดตัวครั้งแรกโดย ST ในปี 1986 เทคโนโลยีนี้สามารถสร้างอุปกรณ์ไบโพลาร์ CMOS และ DMOS บนชิปตัวเดียวกันได้ รูปลักษณ์ของเทคโนโลยีนี้ช่วยลดพื้นที่ของชิปได้อย่างมาก

กล่าวได้ว่ากระบวนการ BCD ใช้ประโยชน์จากข้อดีของความสามารถในการขับเคลื่อนแบบไบโพลาร์ การผสานรวม CMOS สูงและการใช้พลังงานต่ำ และความจุของกระแสไฟฟ้าแรงดันสูงและกระแสสูงของ DMOS ได้อย่างเต็มที่ DMOS ถือเป็นกุญแจสำคัญในการปรับปรุงพลังงานและการผสานรวม ด้วยการพัฒนาเพิ่มเติมของเทคโนโลยีวงจรรวม กระบวนการ BCD จึงกลายเป็นเทคโนโลยีการผลิตหลักของ PMIC

ไดอะแกรมตัดขวางกระบวนการ BCD เครือข่ายต้นทาง ขอบคุณ

ข้อดีของกระบวนการ BCD

กระบวนการ BCD ทำให้อุปกรณ์ไบโพลาร์ อุปกรณ์ CMOS และอุปกรณ์จ่ายไฟ DMOS อยู่บนชิปเดียวกันในเวลาเดียวกัน โดยผสานความสามารถในการถ่ายโอนสูงและความสามารถในการขับเคลื่อนโหลดที่แข็งแกร่งของอุปกรณ์ไบโพลาร์ รวมถึงการผสานรวมสูงและการใช้พลังงานต่ำของ CMOS เพื่อให้อุปกรณ์เหล่านี้สามารถเสริมซึ่งกันและกันและใช้ประโยชน์จากข้อดีที่เกี่ยวข้องได้อย่างเต็มที่ ในเวลาเดียวกัน DMOS สามารถทำงานในโหมดสวิตชิ่งด้วยการใช้พลังงานที่ต่ำมาก กล่าวโดยย่อ การใช้พลังงานต่ำ ประสิทธิภาพการใช้พลังงานสูง และการผสานรวมสูงเป็นหนึ่งในข้อได้เปรียบหลักของ BCD กระบวนการ BCD สามารถลดการใช้พลังงานได้อย่างมาก ปรับปรุงประสิทธิภาพของระบบ และมีความน่าเชื่อถือที่ดีขึ้น ฟังก์ชันของผลิตภัณฑ์อิเล็กทรอนิกส์เพิ่มขึ้นทุกวัน และข้อกำหนดสำหรับการเปลี่ยนแปลงแรงดันไฟฟ้า การป้องกันตัวเก็บประจุ และการยืดอายุแบตเตอรี่ก็มีความสำคัญเพิ่มมากขึ้น ลักษณะความเร็วสูงและประหยัดพลังงานของ BCD ตอบสนองข้อกำหนดของกระบวนการสำหรับชิปการจัดการพลังงาน/อะนาล็อกประสิทธิภาพสูง

เทคโนโลยีหลักของกระบวนการ BCD

อุปกรณ์ทั่วไปของกระบวนการ BCD ได้แก่ CMOS แรงดันไฟต่ำ หลอด MOS แรงดันสูง LDMOS ที่มีแรงดันพังทลายต่างๆ NPN/PNP แนวตั้ง และไดโอด Schottky เป็นต้น กระบวนการบางอย่างยังรวมอุปกรณ์ เช่น JFET และ EEPROM เข้าด้วยกัน ส่งผลให้มีอุปกรณ์ที่หลากหลายในกระบวนการ BCD ดังนั้น นอกเหนือจากการพิจารณาความเข้ากันได้ของอุปกรณ์แรงดันไฟสูงและอุปกรณ์แรงดันไฟต่ำ กระบวนการดับเบิลคลิก และกระบวนการ CMOS เป็นต้น ในการออกแบบแล้ว ยังต้องพิจารณาเทคโนโลยีการแยกที่เหมาะสมด้วย

ในเทคโนโลยีการแยก BCD มีเทคโนโลยีต่างๆ มากมาย เช่น การแยกทางแยก การแยกตัวเอง และการแยกทางไดอิเล็กทริก เกิดขึ้นอย่างต่อเนื่อง เทคโนโลยีการแยกทางแยกคือการสร้างอุปกรณ์บนชั้นเอพิแทกเซียลชนิด N ของซับสเตรตชนิด P และใช้ลักษณะไบอัสย้อนกลับของรอยต่อ PN เพื่อให้เกิดการแยก เนื่องจากรอยต่อ PN มีความต้านทานสูงมากภายใต้ไบอัสย้อนกลับ

เทคโนโลยีการแยกตัวเองนั้นโดยพื้นฐานแล้วคือการแยก PN junction ซึ่งอาศัยลักษณะ PN junction ตามธรรมชาติระหว่างบริเวณต้นทางและบริเวณเดรนของอุปกรณ์และซับสเตรตเพื่อให้เกิดการแยก เมื่อเปิดหลอด MOS บริเวณต้นทาง บริเวณเดรน และช่องสัญญาณจะถูกล้อมรอบด้วยบริเวณ depletion ทำให้เกิดการแยกจากซับสเตรต เมื่อปิดหลอด MOS PN junction ระหว่างบริเวณเดรนและซับสเตรตจะมีอคติย้อนกลับ และแรงดันไฟฟ้าสูงของบริเวณต้นทางจะถูกแยกโดยบริเวณ depletion

การแยกตัวแบบไดอิเล็กทริกใช้สื่อฉนวน เช่น ซิลิกอนออกไซด์เพื่อให้เกิดการแยกตัว โดยอาศัยการแยกตัวแบบไดอิเล็กทริกและการแยกตัวต่อ การแยกตัวแบบไดอิเล็กทริกกึ่งๆ ได้รับการพัฒนาโดยผสมผสานข้อดีของทั้งสองอย่างเข้าด้วยกัน ด้วยการนำเทคโนโลยีการแยกตัวข้างต้นมาใช้อย่างเลือกสรร จึงสามารถใช้งานร่วมกันได้ทั้งแรงดันไฟฟ้าสูงและแรงดันไฟฟ้าต่ำ

ทิศทางการพัฒนากระบวนการ BCD

การพัฒนาเทคโนโลยีกระบวนการ BCD นั้นไม่เหมือนกับกระบวนการ CMOS มาตรฐาน ซึ่งปฏิบัติตามกฎของมัวร์มาโดยตลอดในการพัฒนาไปในทิศทางของความกว้างของเส้นที่เล็กลงและความเร็วที่เร็วขึ้น กระบวนการ BCD มีความแตกต่างและพัฒนาไปในสามทิศทาง ได้แก่ แรงดันไฟฟ้าสูง กำลังไฟฟ้าสูง และความหนาแน่นสูง

1.ทิศทาง BCD แรงดันสูง

BCD แรงดันสูงสามารถผลิตวงจรควบคุมแรงดันต่ำที่มีความน่าเชื่อถือสูงและวงจรระดับ DMOS แรงดันสูงพิเศษบนชิปเดียวกันได้ในเวลาเดียวกัน และสามารถผลิตอุปกรณ์แรงดันสูง 500-700V ได้ อย่างไรก็ตาม โดยทั่วไป BCD ยังคงเหมาะสำหรับผลิตภัณฑ์ที่มีความต้องการอุปกรณ์ไฟฟ้าค่อนข้างสูง โดยเฉพาะอุปกรณ์ BJT หรือ DMOS กระแสไฟสูง และสามารถใช้สำหรับการควบคุมกำลังไฟในระบบไฟส่องสว่างอิเล็กทรอนิกส์และการใช้งานในอุตสาหกรรม

เทคโนโลยีปัจจุบันสำหรับการผลิต BCD แรงดันสูงคือเทคโนโลยี RESURF ที่เสนอโดย Appel et al. ในปี 1979 อุปกรณ์นี้ผลิตขึ้นโดยใช้ชั้นเอพิแทกเซียลที่มีการเจือปนเล็กน้อยเพื่อให้การกระจายของสนามไฟฟ้าบนพื้นผิวราบเรียบขึ้น จึงช่วยปรับปรุงลักษณะการพังทลายบนพื้นผิว ทำให้การพังทลายเกิดขึ้นที่ตัวเครื่องแทนที่จะเป็นบนพื้นผิว จึงทำให้แรงดันพังทลายของอุปกรณ์เพิ่มขึ้น การเจือปนเล็กน้อยเป็นอีกวิธีหนึ่งในการเพิ่มแรงดันพังทลายของ BCD โดยส่วนใหญ่ใช้การระบายแบบกระจายคู่ DDD (การระบายแบบเจือปนคู่) และการระบายแบบเจือปนเล็กน้อย LDD (การระบายแบบเจือปนเล็กน้อย) ในบริเวณการระบาย DMOS จะมีการเพิ่มบริเวณดริฟท์ประเภท N เพื่อเปลี่ยนการสัมผัสเดิมระหว่างการระบาย N+ และสารตั้งต้นประเภท P ให้เป็นการสัมผัสระหว่างการระบาย N- และการระบาย P- จึงทำให้แรงดันพังทลายเพิ่มขึ้น

2. BCD ทิศทางกำลังสูง

ช่วงแรงดันไฟฟ้าของ BCD กำลังสูงคือ 40-90V และส่วนใหญ่ใช้ในอุปกรณ์อิเล็กทรอนิกส์ยานยนต์ที่ต้องการความสามารถในการขับเคลื่อนกระแสไฟฟ้าสูง แรงดันไฟฟ้าปานกลาง และวงจรควบคุมแบบง่าย ลักษณะที่ต้องการคือความสามารถในการขับเคลื่อนกระแสไฟฟ้าสูง แรงดันไฟฟ้าปานกลาง และวงจรควบคุมมักจะค่อนข้างง่าย

3.ทิศทาง BCD ความหนาแน่นสูง

BCD ความหนาแน่นสูง มีช่วงแรงดันไฟฟ้าตั้งแต่ 5-50V และอุปกรณ์อิเล็กทรอนิกส์ยานยนต์บางประเภทจะมีแรงดันไฟฟ้าถึง 70V สามารถรวมฟังก์ชันที่ซับซ้อนและหลากหลายมากขึ้นไว้ในชิปเดียวกันได้ BCD ความหนาแน่นสูงใช้แนวคิดการออกแบบแบบแยกส่วนบางส่วนเพื่อให้เกิดการกระจายผลิตภัณฑ์ โดยส่วนใหญ่ใช้ในแอปพลิเคชันอิเล็กทรอนิกส์ยานยนต์

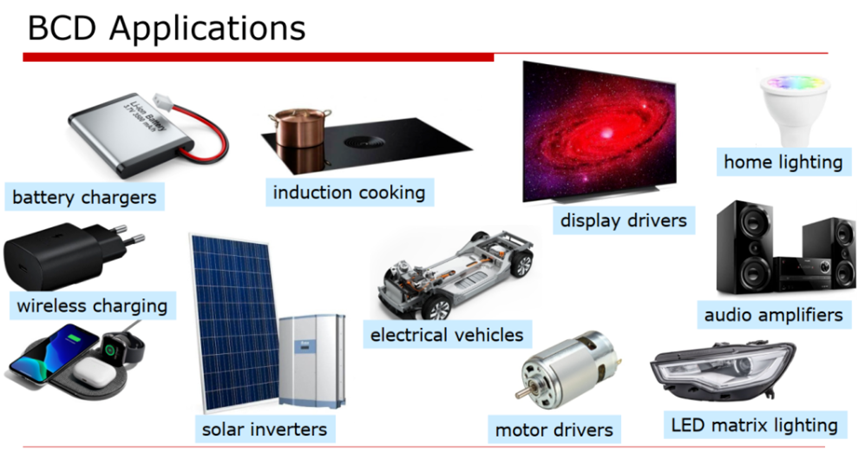

การใช้งานหลักของกระบวนการ BCD

กระบวนการ BCD ใช้กันอย่างแพร่หลายในการจัดการพลังงาน (การควบคุมพลังงานและแบตเตอรี่) ไดรฟ์จอแสดงผล อิเล็กทรอนิกส์ยานยนต์ การควบคุมอุตสาหกรรม ฯลฯ ชิปการจัดการพลังงาน (PMIC) เป็นหนึ่งในประเภทชิปแอนะล็อกที่สำคัญ การผสมผสานระหว่างกระบวนการ BCD และเทคโนโลยี SOI ยังเป็นคุณลักษณะสำคัญของการพัฒนากระบวนการ BCD

VET-China สามารถจัดหาชิ้นส่วนกราไฟต์ แผ่นสักหลาดแข็ง ชิ้นส่วนซิลิกอนคาร์ไบด์ ชิ้นส่วนซิลิกอนคาร์ไบด์ CVD และชิ้นส่วนเคลือบ SIC/TAC ได้ภายใน 30 วัน

หากคุณสนใจผลิตภัณฑ์เซมิคอนดักเตอร์ข้างต้นโปรดอย่าลังเลที่จะติดต่อเราในครั้งแรก

โทรศัพท์:+86-1891 1596 392

วอทส์แอพ:86-18069021720

อีเมล:yeah@china-vet.com

เวลาโพสต์ : 18-9-2024