Was ist der BCD-Prozess?

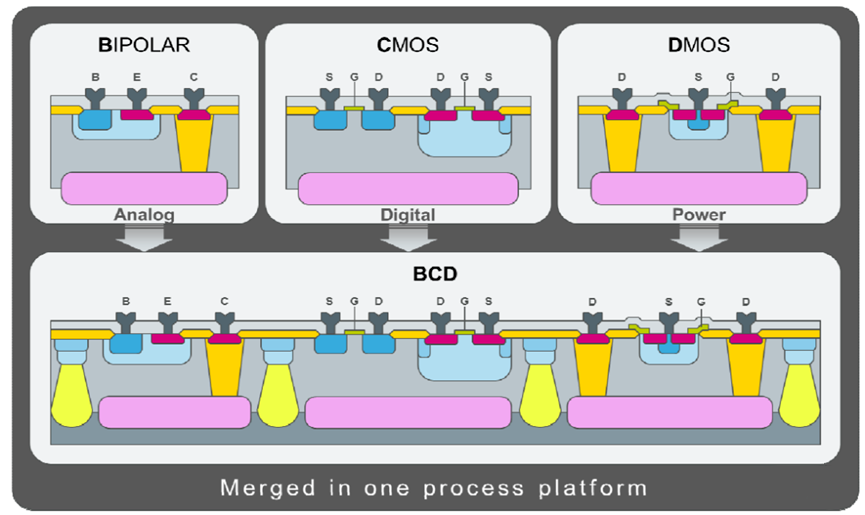

Der BCD-Prozess ist eine integrierte Einzelchip-Prozesstechnologie, die erstmals 1986 von ST eingeführt wurde. Mit dieser Technologie können bipolare, CMOS- und DMOS-Bauelemente auf demselben Chip hergestellt werden. Ihr Erscheinungsbild reduziert die Chipfläche erheblich.

Man kann sagen, dass das BCD-Verfahren die Vorteile der bipolaren Ansteuerung, der hohen Integration und des geringen Stromverbrauchs von CMOS sowie der hohen Spannung und Stromflusskapazität von DMOS voll ausschöpft. DMOS ist dabei der Schlüssel zur Verbesserung von Leistung und Integration. Mit der Weiterentwicklung der integrierten Schaltkreistechnologie hat sich das BCD-Verfahren zur gängigen Fertigungstechnologie für PMICs entwickelt.

BCD-Prozessquerschnittsdiagramm, Quellnetzwerk, danke

Vorteile des BCD-Prozesses

Das BCD-Verfahren ermöglicht die gleichzeitige Integration von bipolaren, CMOS- und DMOS-Leistungsbauelementen auf demselben Chip. Dabei werden die hohe Steilheit und die hohe Lastansteuerfähigkeit bipolarer Bauelemente mit der hohen Integrationsdichte und dem geringen Stromverbrauch von CMOS kombiniert, sodass sich die Bauelemente ergänzen und ihre jeweiligen Vorteile voll ausspielen können. Gleichzeitig kann DMOS im Schaltmodus mit extrem geringem Stromverbrauch arbeiten. Kurz gesagt: Geringer Stromverbrauch, hohe Energieeffizienz und hohe Integrationsdichte sind die Hauptvorteile von BCD. Das BCD-Verfahren kann den Stromverbrauch deutlich senken, die Systemleistung verbessern und die Zuverlässigkeit steigern. Die Funktionen elektronischer Produkte nehmen täglich zu und die Anforderungen an Spannungsänderungen, Kondensatorschutz und eine längere Batterielebensdauer werden immer wichtiger. Die hohen Geschwindigkeits- und Energiespareigenschaften von BCD erfüllen die Prozessanforderungen für leistungsstarke Analog-/Power-Management-Chips.

Schlüsseltechnologien des BCD-Prozesses

Typische Bauelemente im BCD-Prozess sind Niederspannungs-CMOS, Hochspannungs-MOS-Röhren, LDMOS mit unterschiedlichen Durchbruchspannungen, vertikale NPN/PNP- und Schottky-Dioden usw. Einige Prozesse integrieren auch Bauelemente wie JFET und EEPROM, was zu einer großen Bauelementvielfalt im BCD-Prozess führt. Daher muss beim Design neben der Kompatibilität von Hochspannungs- und Niederspannungsbauelementen, Double-Click-Prozessen und CMOS-Prozessen usw. auch die geeignete Isolationstechnologie berücksichtigt werden.

In der BCD-Isolationstechnologie sind nach und nach viele Technologien wie Sperrschichtisolation, Selbstisolation und dielektrische Isolation entstanden. Bei der Sperrschichtisolationstechnologie wird das Gerät auf der N-Typ-Epitaxieschicht des P-Typ-Substrats hergestellt und die Sperrspannungseigenschaften der PN-Verbindung zur Isolierung genutzt, da die PN-Verbindung unter Sperrspannung einen sehr hohen Widerstand aufweist.

Die Selbstisolationstechnologie ist im Wesentlichen eine PN-Übergangsisolierung. Sie nutzt die natürlichen PN-Übergangseigenschaften zwischen den Source- und Drain-Bereichen des Bauelements und dem Substrat zur Isolierung. Im eingeschalteten Zustand der MOS-Röhre sind Source-Bereich, Drain-Bereich und Kanal von der Verarmungszone umgeben und bilden so eine Isolation zum Substrat. Im ausgeschalteten Zustand ist der PN-Übergang zwischen Drain-Bereich und Substrat in Sperrrichtung vorgespannt, und die hohe Spannung des Source-Bereichs wird durch die Verarmungszone isoliert.

Die dielektrische Isolierung nutzt isolierende Medien wie Siliziumoxid. Basierend auf dielektrischer Isolierung und Sperrschichtisolierung wurde die quasi-dielektrische Isolierung entwickelt, die die Vorteile beider Technologien kombiniert. Durch den gezielten Einsatz der oben genannten Isolationstechnologie kann Hochspannungs- und Niederspannungskompatibilität erreicht werden.

Entwicklungsrichtung des BCD-Prozesses

Die Entwicklung der BCD-Prozesstechnologie unterscheidet sich vom Standard-CMOS-Prozess, der sich stets nach dem Mooreschen Gesetz in Richtung kleinerer Linienbreiten und höherer Geschwindigkeit entwickelt hat. Der BCD-Prozess wird grob in drei Richtungen unterschieden und entwickelt: hohe Spannung, hohe Leistung und hohe Dichte.

1. Hochspannungs-BCD-Richtung

Mit Hochspannungs-BCD lassen sich hochzuverlässige Niederspannungs-Steuerschaltungen und Ultrahochspannungs-DMOS-Schaltungen gleichzeitig auf demselben Chip herstellen und Hochspannungsbauelemente mit 500–700 V herstellen. Generell eignet sich BCD jedoch weiterhin für Produkte mit relativ hohen Anforderungen an Leistungsbauelemente, insbesondere BJT- oder Hochstrom-DMOS-Bauelemente, und kann zur Leistungssteuerung in elektronischen Beleuchtungs- und Industrieanwendungen eingesetzt werden.

Die aktuelle Technologie zur Herstellung von Hochspannungs-BCDs ist die 1979 von Appel et al. vorgeschlagene RESURF-Technologie. Das Gerät wird unter Verwendung einer leicht dotierten Epitaxieschicht hergestellt, um die elektrische Feldverteilung an der Oberfläche flacher zu machen und dadurch die Durchbrucheigenschaften der Oberfläche zu verbessern, sodass der Durchbruch im Körper statt an der Oberfläche auftritt, wodurch die Durchbruchspannung des Geräts erhöht wird. Leichte Dotierung ist eine weitere Methode zur Erhöhung der Durchbruchspannung von BCD. Dabei werden hauptsächlich doppelt diffundierte Drains (DDD) und leicht dotierte Drains (LDD) verwendet. Im DMOS-Drain-Bereich wird ein N-Typ-Driftbereich hinzugefügt, um den ursprünglichen Kontakt zwischen dem N+-Drain und dem P-Typ-Substrat in den Kontakt zwischen dem N--Drain und dem P-Typ-Substrat zu ändern und dadurch die Durchbruchspannung zu erhöhen.

2. Hochleistungs-BCD-Richtung

Der Spannungsbereich von Hochleistungs-BCDs liegt zwischen 40 und 90 V. Sie werden hauptsächlich in der Automobilelektronik eingesetzt, wo hohe Stromstärken, mittlere Spannungen und einfache Steuerschaltungen erforderlich sind. Die geforderten Eigenschaften sind hohe Stromstärken und mittlere Spannungen, und die Steuerschaltung ist oft relativ einfach.

3. BCD-Richtung mit hoher Dichte

Hochdichte BCDs haben einen Spannungsbereich von 5–50 V, wobei einige Automobilelektroniken bis zu 70 V erreichen. Immer komplexere und vielfältigere Funktionen können auf demselben Chip integriert werden. Hochdichte BCDs nutzen modulare Designideen zur Produktdiversifizierung und werden hauptsächlich in der Automobilelektronik eingesetzt.

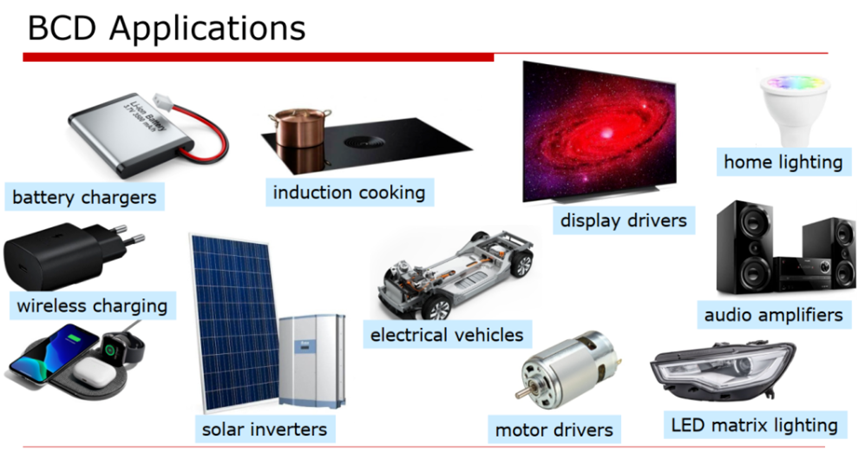

Hauptanwendungen des BCD-Prozesses

Das BCD-Verfahren wird häufig im Energiemanagement (Strom- und Batteriesteuerung), in Display-Ansteuerungen, der Automobilelektronik und der industriellen Steuerung eingesetzt. Der Energiemanagement-Chip (PMIC) ist ein wichtiger Typ analoger Chips. Die Kombination aus BCD-Verfahren und SOI-Technologie ist ein weiteres wichtiges Merkmal der BCD-Entwicklung.

VET-China kann Graphitteile, Weichfilz, Siliziumkarbidteile, CVD-Siliziumkarbidteile und Sic/Tac-beschichtete Teile innerhalb von 30 Tagen liefern.

Wenn Sie an den oben genannten Halbleiterprodukten interessiert sind, zögern Sie bitte nicht, uns umgehend zu kontaktieren.

Tel:+86-1891 1596 392

WhatsApp: 86-18069021720

E-Mail:yeah@china-vet.com

Veröffentlichungszeit: 18. September 2024