BCD プロセスとは何ですか?

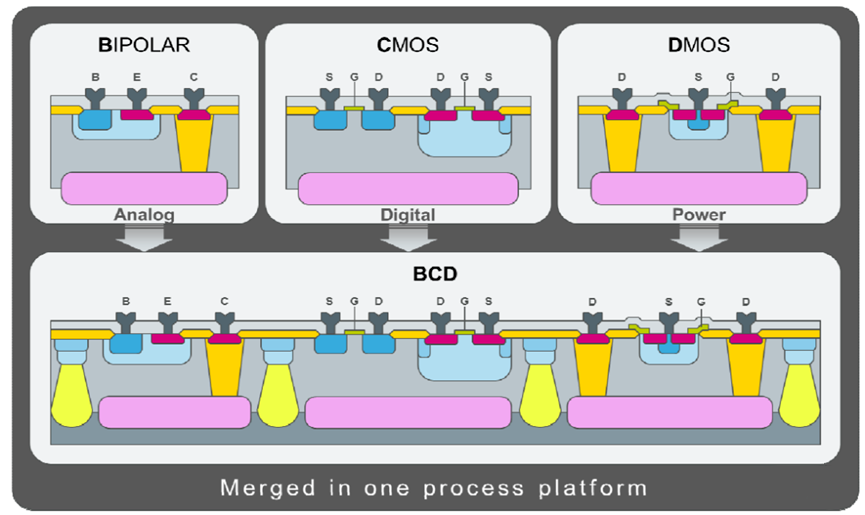

BCDプロセスは、STが1986年に初めて導入したシングルチップ統合プロセス技術です。この技術により、バイポーラ、CMOS、DMOSデバイスを同一チップ上に集積化することができ、チップ面積を大幅に削減できます。

BCDプロセスは、バイポーラ駆動能力、CMOSの高集積・低消費電力、DMOSの高耐圧・大電流容量といった利点を最大限に活用していると言えます。中でもDMOSは、消費電力と集積度の向上の鍵となります。集積回路技術のさらなる発展に伴い、BCDプロセスはPMICの主流製造技術となっています。

BCDプロセス断面図、ソースネットワーク、ありがとうございます

BCDプロセスの利点

BCDプロセスは、バイポーラデバイス、CMOSデバイス、およびDMOSパワーデバイスを同じチップ上で同時に製造し、バイポーラデバイスの高いトランスコンダクタンスと強力な負荷駆動能力と、CMOSの高集積度と低消費電力を統合することで、それらが互いに補完し、それぞれの利点を十分に発揮できるようにします。同時に、DMOSは、非常に低い消費電力でスイッチングモードで動作できます。つまり、低消費電力、高エネルギー効率、および高集積度は、BCDの主な利点の1つです。BCDプロセスは、消費電力を大幅に削減し、システムパフォーマンスを向上させ、信頼性を向上させます。電子製品の機能は日々増加しており、電圧変更、コンデンサ保護、およびバッテリ寿命の延長に対する要件はますます重要になっています。BCDの高速性と省エネ特性は、高性能アナログ/電源管理チップのプロセス要件を満たしています。

BCDプロセスの主要技術

BCDプロセスの代表的なデバイスには、低電圧CMOS、高電圧MOSトランジスタ、様々なブレークダウン電圧のLDMOS、縦型NPN/PNP、ショットキーダイオードなどがあります。一部のプロセスではJFETやEEPROMなどのデバイスも統合されており、BCDプロセスには多種多様なデバイスが存在します。そのため、設計においては、高電圧デバイスと低電圧デバイス、ダブルクリックプロセスとCMOSプロセスなどの互換性を考慮するだけでなく、適切な分離技術も考慮する必要があります。

BCD分離技術では、接合分離、自己分離、誘電体分離など、様々な技術が次々と登場しています。接合分離技術は、P型基板上のN型エピタキシャル層上にデバイスを作製し、PN接合の逆バイアス特性を利用して分離を実現するものです。PN接合は逆バイアス下で非常に高い抵抗値を示すためです。

自己分離技術は本質的にPN接合分離であり、デバイスのソース・ドレイン領域と基板との間の自然なPN接合特性を利用して分離を実現します。MOSトランジスタがオンになると、ソース領域、ドレイン領域、チャネルは空乏領域に囲まれ、基板との分離を形成します。オフになると、ドレイン領域と基板間のPN接合は逆バイアスされ、ソース領域の高電圧は空乏領域によって分離されます。

誘電体分離は、シリコン酸化物などの絶縁媒体を用いて分離を実現します。誘電体分離と接合分離をベースに、両者の利点を組み合わせた擬似誘電体分離が開発されました。これらの分離技術を選択的に採用することで、高電圧と低電圧の両立を実現できます。

BCDプロセスの開発方向

BCDプロセス技術の開発は、ムーアの法則に従って常に線幅の縮小と高速化の方向に発展してきた標準的なCMOSプロセスとは異なります。BCDプロセスは、高電圧、高電力、高密度という3つの方向に大別され、発展しています。

1.高電圧BCD方向

高電圧BCDは、高信頼性の低電圧制御回路と超高電圧DMOSレベル回路を同一チップ上に同時に製造することができ、500~700Vの高電圧デバイスの製造を実現します。しかし、一般的にBCDは、パワーデバイス、特にBJTや大電流DMOSデバイスに対する要求が比較的高い製品に適しており、電子照明や産業用途における電力制御に使用できます。

高電圧BCDを製造する現在の技術は、1979年にAppelらが提案したRESURF技術である。このデバイスは、軽くドープされたエピタキシャル層を使用して製造され、表面電界分布をより平坦化することで表面ブレークダウン特性を改善し、ブレークダウンが表面ではなく本体で発生するため、デバイスのブレークダウン電圧が向上します。 ライトドーピングは、BCDのブレークダウン電圧を上げるもう1つの方法です。主に二重拡散ドレインDDD(ダブルドーピングドレイン)と軽くドープされたドレインLDD(ライトドーピングドレイン)を使用します。 DMOSドレイン領域では、N型ドリフト領域が追加され、N +ドレインとP型基板間の元の接触がN-ドレインとP型基板間の接触に変更され、ブレークダウン電圧が向上します。

2.高出力BCD方向

高出力BCDの電圧範囲は40~90Vで、主に車載エレクトロニクス分野で使用され、高電流駆動能力、中電圧、シンプルな制御回路が求められます。その要求特性は、高電流駆動能力、中電圧、そして比較的シンプルな制御回路です。

3. 高密度BCD方向

高密度BCDの電圧範囲は5~50Vですが、一部の車載エレクトロニクスでは70Vに達します。より複雑で多様な機能を同一チップに統合することが可能です。高密度BCDは、製品の多様化を実現するためにモジュール設計を採用しており、主に車載エレクトロニクス用途に使用されています。

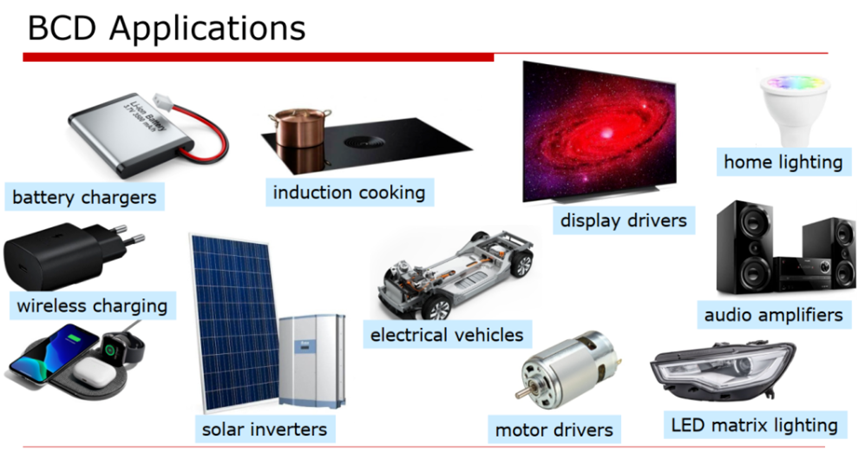

BCDプロセスの主な用途

BCDプロセスは、電力管理(電源およびバッテリー制御)、ディスプレイ駆動、車載エレクトロニクス、産業用制御などに広く利用されています。電源管理チップ(PMIC)は、アナログチップの重要な種類の一つです。BCDプロセスとSOI技術の組み合わせも、BCDプロセス開発の大きな特徴です。

VET-China は、グラファイト部品、ソフトリジッドフェルト、シリコンカーバイド部品、CVD シリコンカーバイド部品、および sic/Tac コーティング部品を 30 日以内に提供できます。

上記半導体製品にご興味がございましたら、まずはお気軽にお問い合わせください。

電話:+86-1891 1596 392

WhatsApp:86-18069021720

メールアドレス:yeah@china-vet.com

投稿日時: 2024年9月18日