CVD SiC 코팅이란?

화학 기상 증착(CVD)은 고순도 고체 물질을 생산하는 데 사용되는 진공 증착 공정입니다. 이 공정은 반도체 제조 분야에서 웨이퍼 표면에 박막을 형성하는 데 자주 사용됩니다. CVD를 이용하여 탄화규소를 제조하는 공정에서, 기판은 하나 이상의 휘발성 전구체에 노출되고, 이 전구체는 기판 표면에서 화학적으로 반응하여 원하는 탄화규소를 증착합니다. 탄화규소 물질을 제조하는 여러 방법 중 화학 기상 증착으로 제조된 제품은 균일성과 순도가 더 높으며, 공정 제어성이 뛰어납니다. CVD 실리콘 카바이드 소재는 뛰어난 열적, 전기적, 화학적 특성의 독특한 조합을 지니고 있어 고성능 소재가 요구되는 반도체 산업에 매우 적합합니다. CVD 실리콘 카바이드 부품은 에칭 장비, MOCVD 장비, Si 에피택셜 장비 및 SiC 에피택셜 장비, 고속 열처리 장비 등 다양한 분야에서 널리 사용됩니다.

이 기사는 제조 중 다양한 공정 온도에서 성장된 박막의 품질을 분석하는 데 중점을 둡니다.CVD SiC 코팅, 가장 적합한 공정 온도를 선택하기 위해. 실험은 흑연을 기판으로, 트리클로로메틸실란(MTS)을 반응 소스 가스로 사용합니다. SiC 코팅은 저압 CVD 공정으로 증착되며, 미세 형태는CVD SiC 코팅주사전자현미경으로 관찰하여 구조적 밀도를 분석합니다.

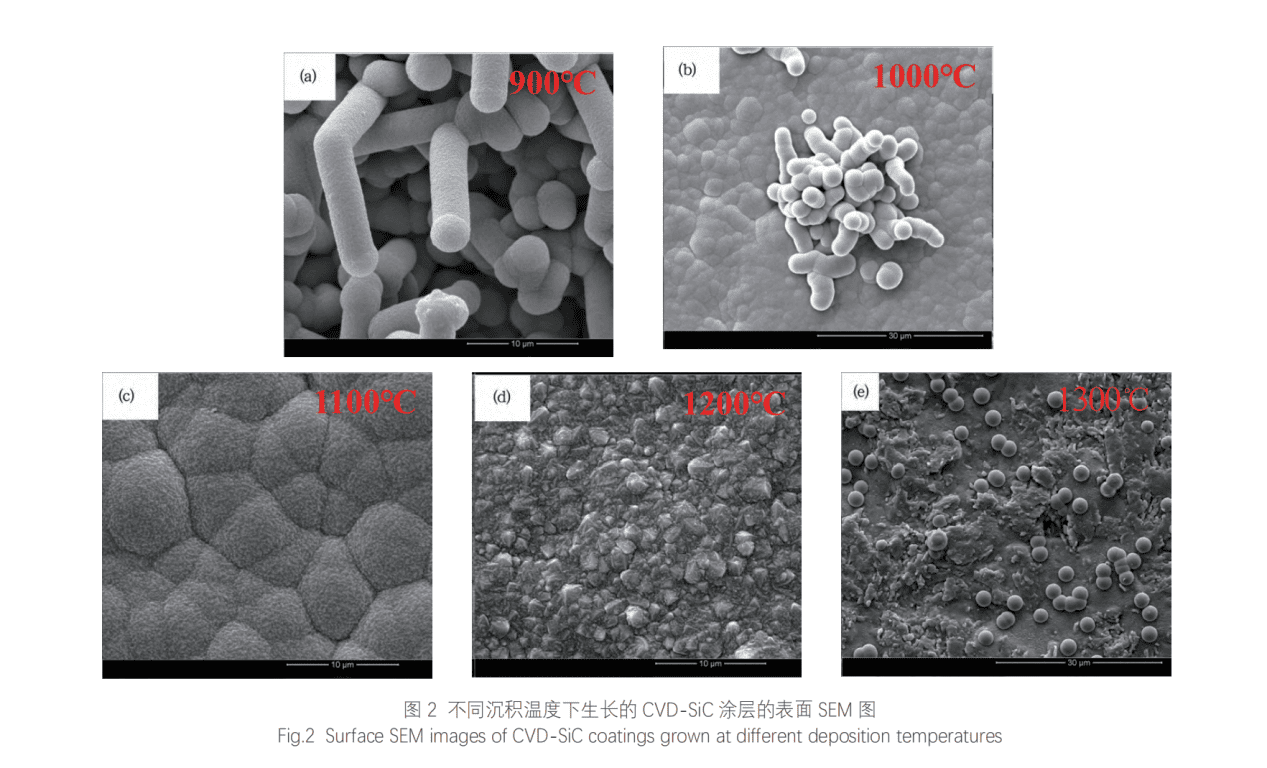

흑연 기판의 표면 온도가 매우 높기 때문에 중간 가스가 기판 표면에서 탈착 및 배출되고, 최종적으로 기판 표면에 남아 있는 C와 Si가 고체상 SiC를 형성하여 SiC 코팅을 형성합니다.위의 CVD-SiC 성장 공정에 따르면, 온도가 가스 확산, MTS의 분해, 액적 형성 및 중간 가스의 탈착 및 배출에 영향을 미치므로 증착 온도가 SiC 코팅의 형태에 중요한 역할을 함을 알 수 있습니다.코팅의 미시적 형태는 코팅 밀도를 가장 직관적으로 나타냅니다.따라서 CVD SiC 코팅의 미시적 형태에 대한 다양한 증착 온도의 영향을 연구할 필요가 있습니다. MTS는 900~1600℃ 사이에서 SiC 코팅을 분해 및 증착할 수 있으므로, 본 실험에서는 CVD-SiC 코팅에 대한 온도의 영향을 연구하기 위해 900℃, 1000℃, 1100℃, 1200℃, 1300℃의 다섯 가지 증착 온도를 선택하여 SiC 코팅을 제조했습니다. 구체적인 매개변수는 표 3에 제시되어 있습니다. 그림 2는 다양한 증착 온도에서 성장된 CVD-SiC 코팅의 미세 형태를 보여줍니다.

증착 온도가 900℃일 때, 모든 SiC는 섬유 모양으로 성장합니다. 단일 섬유의 직경은 약 3.5μm이고, 종횡비는 약 3(<10)임을 알 수 있습니다. 또한, 무수한 나노 SiC 입자로 구성되어 다결정 SiC 구조에 속하며, 이는 기존의 SiC 나노와이어 및 단결정 SiC 위스커와는 다릅니다. 이 섬유형 SiC는 불합리한 공정 변수로 인해 발생하는 구조적 결함입니다. 이 SiC 코팅의 구조는 비교적 느슨하고, 섬유형 SiC 사이에 많은 기공이 있으며, 밀도가 매우 낮음을 알 수 있습니다. 따라서 이 온도는 고밀도 SiC 코팅을 제조하기에 적합하지 않습니다. 일반적으로 섬유형 SiC 구조적 결함은 증착 온도가 너무 낮아 발생합니다. 낮은 온도에서는 기판 표면에 흡착된 작은 분자의 에너지가 낮아 이동 능력이 저하됩니다. 따라서 작은 분자들은 SiC 입자의 표면 자유 에너지가 가장 낮은 지점(예: 입자 끝부분)으로 이동하여 성장하는 경향이 있습니다. 이러한 지속적인 방향성 성장은 결국 섬유질 SiC 구조 결함을 형성합니다.

CVD SiC 코팅 준비:

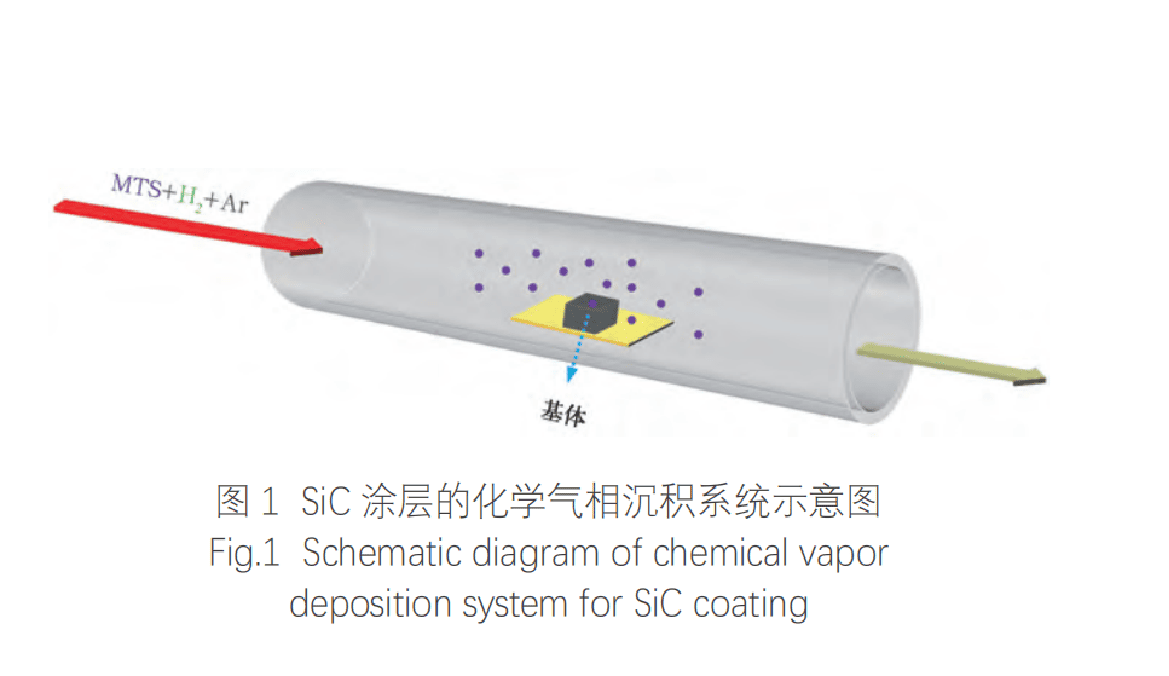

먼저, 흑연 기판을 고온 진공로에 넣고 1500℃에서 1시간 동안 Ar 분위기에서 유지하여 재를 제거합니다. 그런 다음 흑연 블록을 15x15x5mm 크기의 블록으로 절단하고, 1200메시 사포로 표면을 연마하여 SiC 증착에 영향을 미치는 표면 기공을 제거합니다. 처리된 흑연 블록을 무수 에탄올과 증류수로 세척한 후 100℃ 오븐에서 건조합니다. 마지막으로, 흑연 기판을 SiC 증착을 위해 관형로의 주요 온도 영역에 놓습니다. 화학 기상 증착 시스템의 개략도는 그림 1에 나와 있습니다.

그만큼CVD SiC 코팅주사전자현미경으로 관찰하여 입자 크기와 밀도를 분석했습니다. 또한, SiC 코팅의 증착 속도는 아래 공식에 따라 계산했습니다. VSiC=(m2-m1)/(Sxt)x100% VSiC=증착 속도; m2-코팅 샘플의 질량(mg); m1–기질의 질량(mg); S-기판의 표면적(mm2) t-증착 시간(h). CVD-SiC는 비교적 복잡하며, 공정은 다음과 같이 요약할 수 있습니다. 고온에서 MTS는 열 분해를 거쳐 탄소원과 실리콘원 소분자를 형성합니다. 탄소원 소분자는 주로 CH3, C2H2 및 C2H4를 포함하고 실리콘원 소분자는 주로 SiCl2, SiCl3 등을 포함합니다. 이러한 탄소원과 실리콘원 소분자는 캐리어 가스와 희석 가스에 의해 흑연 기판 표면으로 이동한 후 기판 표면에 흡착 형태로 흡착되고 소분자 간에 화학 반응이 일어나 점차 성장하는 작은 물방울을 형성하고 물방울도 융합하며 반응에는 중간 부산물(HCl 가스)이 형성됩니다. 온도가 1000℃로 상승하면 SiC 코팅의 밀도가 크게 향상됩니다. 대부분의 코팅이 SiC 입자(크기 약 4μm)로 구성되어 있지만 일부 섬유질 SiC 결함도 발견되는데, 이는 이 온도에서 SiC가 방향성 성장을 하고 있고 코팅이 여전히 충분히 조밀하지 않음을 보여줍니다. 온도가 1100℃로 상승하면 SiC 코팅이 매우 조밀해지고 섬유질 SiC 결함이 완전히 사라진 것을 볼 수 있습니다. 코팅은 직경이 약 5~10μm인 물방울 모양의 SiC 입자로 구성되어 있으며 단단히 결합되어 있습니다. 입자의 표면은 매우 거칠고 무수한 나노 크기의 SiC 입자로 구성되어 있습니다. 실제로 1100℃에서의 CVD-SiC 성장 공정은 물질 전달이 제어되었습니다. 기판 표면에 흡착된 작은 분자는 핵을 형성하고 SiC 입자로 성장하기에 충분한 에너지와 시간을 가지고 있습니다. SiC 입자는 균일하게 큰 액적을 형성합니다. 표면 에너지의 작용으로 대부분의 액적은 구형으로 나타나고, 액적들은 서로 밀접하게 결합되어 치밀한 SiC 코팅을 형성합니다. 온도가 1200℃로 상승하면 SiC 코팅도 치밀해지지만, SiC 형태는 여러 갈래로 융기되고 코팅 표면은 거칠어집니다. 온도가 1300℃로 상승하면 흑연 기판 표면에 직경 약 3μm의 규칙적인 구형 입자가 다수 발견됩니다. 이는 이 온도에서 SiC가 기체 핵 생성 상태로 전환되어 MTS 분해 속도가 매우 빠르기 때문입니다. 작은 분자들이 반응하여 핵 생성되어 기판 표면에 흡착되기 전에 SiC 입자를 형성합니다. 입자가 구형 입자를 형성한 후, 그 아래로 떨어져 결국 밀도가 낮은 느슨한 SiC 입자 코팅이 형성됩니다. 1300℃는 치밀한 SiC 코팅의 형성 온도로 사용할 수 없음이 명백합니다. 종합적으로 비교해보면, 치밀한 SiC 코팅을 제조하려면 최적의 CVD 증착 온도는 1100℃입니다.

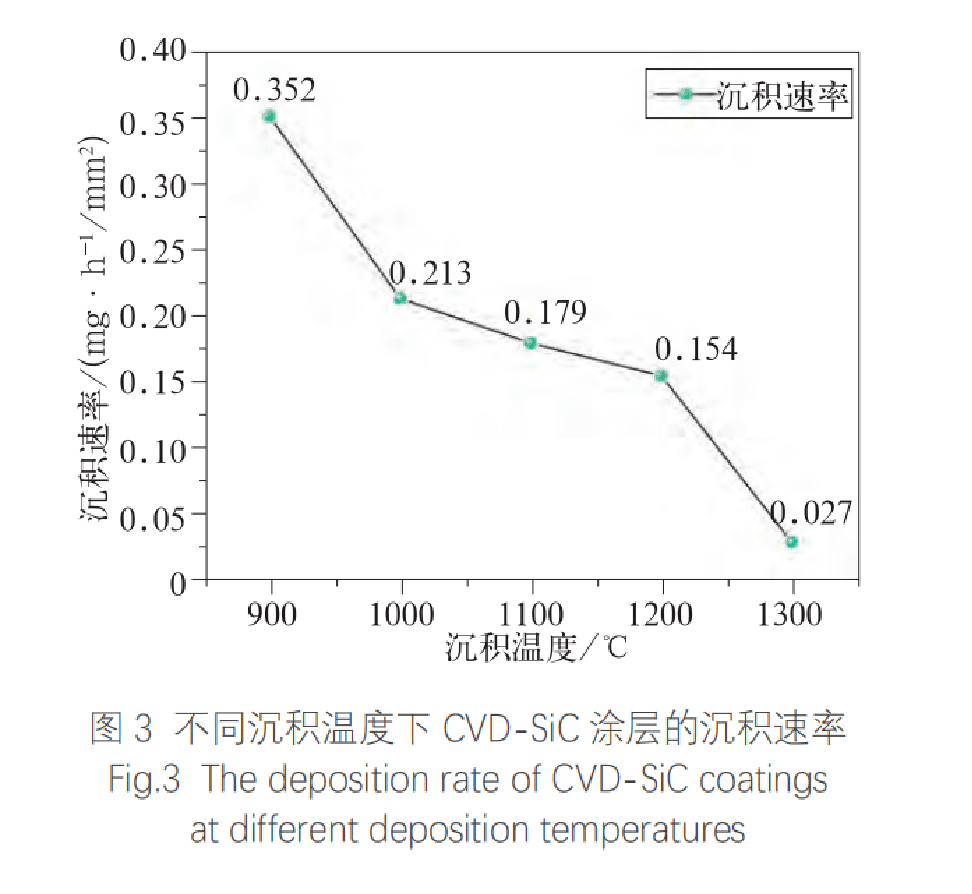

그림 3은 다양한 증착 온도에서 CVD SiC 코팅의 증착 속도를 보여줍니다. 증착 온도가 증가함에 따라 SiC 코팅의 증착 속도는 점차 감소합니다. 900°C에서의 증착 속도는 0.352 mg·h-1/mm²이며, 섬유의 방향성 성장으로 인해 증착 속도가 가장 빠릅니다. 밀도가 가장 높은 코팅의 증착 속도는 0.179 mg·h-1/mm²입니다. 일부 SiC 입자의 증착으로 인해 1300°C에서의 증착 속도는 0.027 mg·h-1/mm²로 가장 낮습니다. 결론: 최적의 CVD 증착 온도는 1100℃입니다. 낮은 온도는 SiC의 방향성 성장을 촉진하는 반면, 높은 온도는 SiC의 기상 증착을 유도하여 성긴 코팅을 형성합니다. 증착 온도가 증가함에 따라 증착 속도는CVD SiC 코팅점차 감소합니다.

게시 시간: 2025년 5월 26일