Der Siliziumkarbid-(SiC)-Epitaxiewafer von VET Energy ist ein Hochleistungs-Halbleitermaterial mit großer Bandlücke und hervorragender Temperaturbeständigkeit sowie hohen Frequenz- und Leistungseigenschaften. Es ist ein ideales Substrat für die neue Generation leistungselektronischer Geräte. VET Energy nutzt fortschrittliche MOCVD-Epitaxietechnologie, um hochwertige SiC-Epitaxieschichten auf SiC-Substraten zu erzeugen und so die hervorragende Leistung und Konsistenz des Wafers zu gewährleisten.

Unser Siliziumkarbid (SiC)-Epitaxie-Wafer bietet hervorragende Kompatibilität mit einer Vielzahl von Halbleitermaterialien, darunter Si-Wafer, SiC-Substrate, SOI-Wafer und SiN-Substrate. Dank seiner robusten Epitaxieschicht unterstützt er fortschrittliche Prozesse wie das Wachstum von Epitaxie-Wafern und die Integration mit Materialien wie Galliumoxid (Ga2O3) und AlN-Wafer und gewährleistet so den vielseitigen Einsatz in verschiedenen Technologien. Er ist kompatibel mit branchenüblichen Kassettenhandhabungssystemen und gewährleistet effiziente und optimierte Abläufe in der Halbleiterfertigung.

Die Produktpalette von VET Energy beschränkt sich nicht nur auf SiC-Epitaxie-Wafer. Wir bieten auch eine breite Palette an Halbleitersubstratmaterialien an, darunter Si-Wafer, SiC-Substrate, SOI-Wafer, SiN-Substrate, Epitaxie-Wafer usw. Darüber hinaus entwickeln wir aktiv neue Halbleitermaterialien mit großem Bandabstand, wie Galliumoxid-Ga2O3 und AlN-Wafer, um den zukünftigen Bedarf der Leistungselektronikindustrie an leistungsstärkeren Bauelementen zu decken.

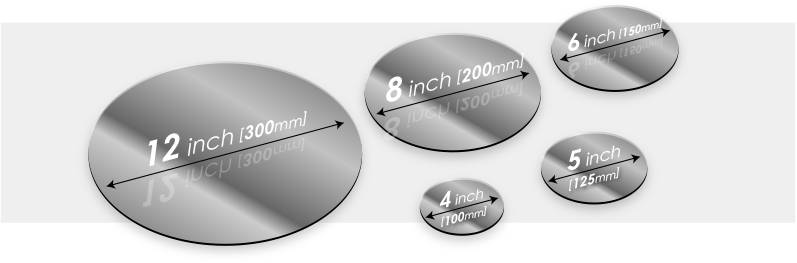

WAFERINGSSPEZIFIKATIONEN

*n-Pm = n-Typ Pm-Grade, n-Ps = n-Typ Ps-Grade, Sl = halbisolierend

| Artikel | 8 Zoll | 6 Zoll | 4 Zoll | ||

| nP | n-Pm | n-Ps | SI | SI | |

| TTV (GBIR) | ≤6 µm | ≤6 µm | |||

| Bow(GF3YFCD)-Absoluter Wert | ≤15μm | ≤15μm | ≤25μm | ≤15μm | |

| Warp (GF3YFER) | ≤25μm | ≤25μm | ≤40μm | ≤25μm | |

| LTV(SBIR)-10mmx10mm | <2 μm | ||||

| Waferkante | Abschrägung | ||||

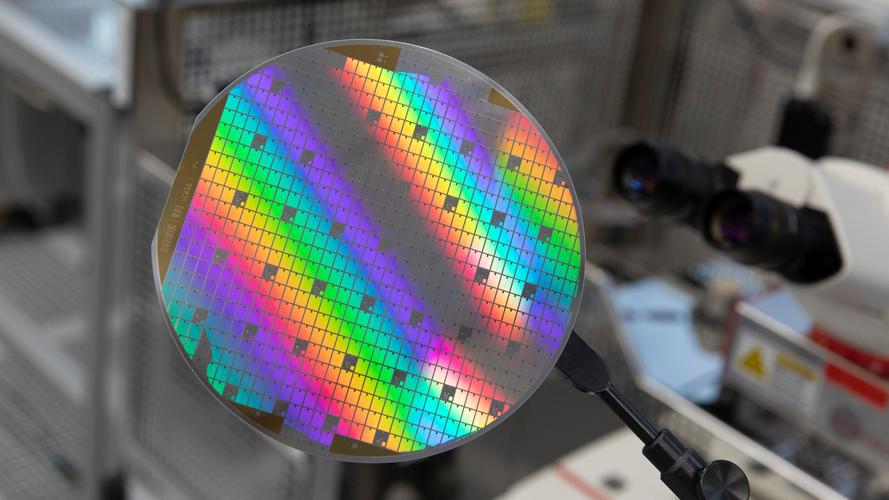

OBERFLÄCHENBEARBEITUNG

*n-Pm = n-Typ Pm-Grade, n-Ps = n-Typ Ps-Grade, Sl = halbisolierend

| Artikel | 8 Zoll | 6 Zoll | 4 Zoll | ||

| nP | n-Pm | n-Ps | SI | SI | |

| Oberflächenbeschaffenheit | Doppelseitige optische Politur, Si-Face CMP | ||||

| Oberflächenrauheit | (10µm x 10µm) Si-FlächeRa≤0,2nm | (5µm x 5µm) Si-Fläche Ra≤0,2nm | |||

| Kantensplitter | Keine zulässig (Länge und Breite ≥ 0,5 mm) | ||||

| Einrückungen | Keine erlaubt | ||||

| Kratzer (Si-Face) | Menge ≤5, kumulativ | Menge ≤5, kumulativ | Menge ≤5, kumulativ | ||

| Risse | Keine erlaubt | ||||

| Kantenausschluss | 3 mm | ||||

-

Brennstoffzelle 1000 W 24 V Drohne Wasserstoff-Brennstoffzellen-Kit

-

Verbrauchsmaterial für Halbleiterausrüstung, Aluminiumoxid-Cer...

-

Mit Graphitstopfen und Harz imprägnierte Axiallager ...

-

Hochfestes Graphit-/Kohlefaserseil für Se...

-

1000-W-PEMF-Stapel-Brennstoffzellenstapel für UAV-PEMF...

-

Oberes und unteres Graphit-Halbmondteil für Si...